# **Der General Electric 645 Computer**

[Die Multics-Architektur]

Maximilian Krüger FAU Erlangen-Nürnberg Martensstraße 1 91058 Erlangen maximilian.krueger@fau.de

### **ABSTRACT**

Diese Seminararbeit gibt einen Überblick über die General Electrics Mainframe Architektur der GE-635, welchen Aufbau sie hatte und welche Veränderungen vorgenommen wurden um aus diesem Rechner die Multics Architektur GE-645 zu machen. Dabei versuche ich zu vermitteln, warum diese Architektur noch heute spannend ist, wo sie unsere heutigen Rechner beeinflusst hat und wo sie ihnen, zumindest in manchen Gesichtspunkten sogar überlegen war.

### 1. EINLEITUNG

Multics<sup>1</sup> war ein sehr ambitioniertes Projekt, welches viele Techniken erprobt hat, die noch heute in der Informatik genutzt werden. Dafür wurde nicht nur ein neues Betriebssystem geschaffen, sondern es brauchte auch speziell dafür modifizierte Computer. Diese Computer waren die GE-645 und ihre Nachfolger. Diese Computer sind gerade deshalb interessant, weil sie ein Musterbeispiel für das darstellen, was wir heute Hardware-Software-Co-Design nennen würden. Auch war die GE-645 ein mindestens so ambitioniertes Projekt wie das Multics Betriebssystem. Zwar sind die meisten der dort verwendeten Konzepte nicht völlig neu, aber in einer Maschine wurden sie zuvor nie vereint. Die Seminararbeit folgt der historischen Entwicklung, angefangen mit der Ursprüngen der GE-600 Serie als Ganzes, gefolgt von den Veränderungen, welche für die Multics-Variante dieser Hardware nötig waren. Abschließend werden noch die weiteren Entwicklungen zusammengefasst.

### 2. ANFORDERUNGEN

Das Multics-Projekt benötigte einen Rechner für das zu entwickelnde Betriebssystem, welcher dafür gezielt angepasst werden sollte. Das Ziel war, ein Betriebssystem mit einem seiten- und segmentbasierten Adressräumen und Mehrbenutzer Zeitscheibenbetrieb zu konstruieren. Als erstes wichtiges Merkmal wurde festgelegt, dass der Rechner einen sau-

ber strukturierten Befehlssatz haben soll, welcher sich für die Verwendung von Hochsprachen und Übersetzern eignet. Zweitens muss der Rechner mehrere Prozessoren unterstützen um parallele Leistung für den interaktiven Mehrbenutzerbetrieb zu bieten. Als dritte und letzte Anforderung wurde ein nicht-synchrones Design gefordert. Dieser Punkt bezieht sich auf die Koppelung einzelner Rechnerkomponenten und stammt aus der Erwartung, dass die geplante Speicherverwaltung sehr langsam sein wird. Ein nicht-synchrones System soll diese Leistungseinbußen so gering wie möglich halten [11].

### 3. GE-635

Am Start des Multics-Projekts wurde der General Electric 635 Computer als Basis für eine eigene Rechnerentwicklung gewählt. Um zu Verstehen, welche Veränderungen für Multics nötig sind, folgt zunächst eine Betrachtung der Basis-Architektur.

### 3.1 Geschichte

General Electric hatte keine lange Erfahrung im Computerbau, sondern hatte vor der GE-600 Serie nur einen Computer entwickelt. Für das militärische MISTRAM Projekt [19] entwickelten sie den M236 Rechner, welcher dort mit IBM 7094 Systemen Daten austauschen sollte. Um dies zu ermöglichen war die M236 ein sehr ähnlicher Entwurf zu dem IBM System. Es war ebenfalls ein 36-Bit Mainframe, welcher aus vielen einzelnen Schränken bestand.

Aus diesem Rechner, der nur für eine einzelne Ausschreibung konstruiert wurde, entwickelte GE im Folgenden die GE-600 Serie. Ursprünglich verfolgte man nur das Ziel den eigenen Bedarf mit diesen Maschinen zu decken, um nicht mehr von IBM abhängig zu sein. Der Plan die GE-600 Serie zu vermarkten entstand erst nachträglich. Zu dieser Serie gehörten die GE-615, GE-625 und die GE-635 wobei die ersten beiden lediglich funktional beschnittene Varianten der GE-635 darstellen. Technisch sind alle drei Rechner, von einigen Kabeln abgesehen identisch und ein Techniker konnte vor Ort eine Aufstockung auf eine der besseren Varianten vor nehmen.

Alle Rechner der GE-600 Serie nutzen das von General Electric selbst entwickelte Betriebssystem GECOS<sup>2</sup> [2].

Neben den GE-600 Mainframes existierte mit der M-600 Serie auch eine militärische Miniaturversion dieses Systems, welches zwar auf Assembler-Ebene kompatibel war, aber deutlich kleiner ausgelegt war[9].

<sup>&</sup>lt;sup>1</sup>Multiplexed Information and Computing Service

<sup>&</sup>lt;sup>2</sup>General Electric Comprehensive Operating Supervisor

Die Ähnlichkeit zu IBM 7094 System war so groß, dass General Electric das "Zusatzgerät" "9SA" anbot, welches die Ausführung von IBM 7094 Code auf einer GE-600 Maschine ermöglichte [5].

# 3.2 Design

Die GE-635 ist Teil der zweiten Generation von Transistorrechnern, welche vollständig aus Transistor-Transistor-Logik (TTL) besteht und nicht wie frühere Systeme aus Widerstands-Transistor-Logik. Der Rechner besteht aus einer Reihe einzelner Schränke, welche sich zu unterschiedlich großen Konfigurationen zusammenstellen lassen. Für die Zeit typisch sind Lochkarten, Lochstreifen und Magnetbänder als Permanentspeicher und Ein-/Ausgabe. Als schnelle Speicher dienen Festplatten und Magnetkern-Ring-Speicher (core memory). Der gesamte Rechner füllte auch in einer kleinen Ausführung schon einen Raum.

### 3.2.1 Struktur

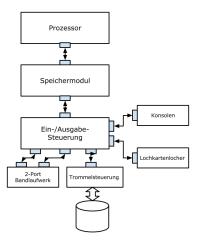

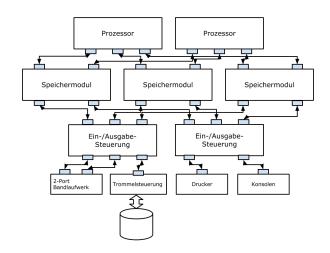

Der Rechner besteht aus drei Kernkomponenten, welche sich in unterschiedlicher Anzahl kombinieren lassen und einer großen Anzahl von oben genannten Peripheriegeräten

Die drei Kernkomponenten sind die Prozessoren, die Ein-/Ausgabe-Steuerung und die Speichermodule. Die Speichermodule sind stellen das zentrale Element des Systems dar und bestehen aus dem System Controller und den eigentlichen Kernspeichern.

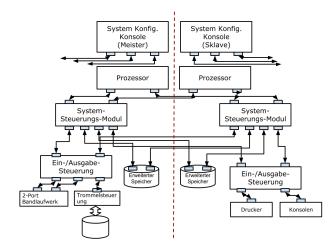

Die Kombination der verschiedenen Komponenten ist im Fall der GE-635 statisch und nicht zur Laufzeit konfigurierbar. Wie das System allerdings Konfiguriert wird ist sehr flexibel. Konfigurationen reichen von einem System aus einem Prozessor, einem Speichermodul und einer Ein-/Ausgabe-Steuerung bis zu Systemen mit 4 Prozessoren und 4 Speichermodulen und daran angeschlossenen Ein-/Ausgabe-Steuereinheiten. Größere Systeme lassen sich dadurch realisieren, dass nicht alle Prozessoren mit allen Speichermodulen verbunden sind, sondern geteilter und privater Speicher existiert. Diese Konfigurationen unterscheiden sind von stark gekoppelten Systemen auch darin, das dort jeder Prozessor auf Ein-/Ausgabe zugreifen kann. In Stark gekoppelten Systemen existiert immer einen Steuerprozessor und alle anderen Prozessoren sind diesem untergeordnet. Stark gekoppelte Systeme werden als Multiprozessor Systeme bezeichnet, während schwach gekoppelte Systeme Multicomputer genannt werden. Zwei beispielhafte Konfigurationen zeigen die Abbildung 1 und Abbildung 2.

Multicomputer haben den Vorzug, dass sich hier einzelne Teilsysteme ausschalten und umkonfigurieren lassen, da sie aus Systemsicht eher mehrere Systeme, welche sich einzelne Kernspeicher teilen sind, als ein festes System.

Die Möglichkeit mehrere Prozessoren in dieser Form zu koppeln war ein neues Konzept und die GE-635 war vermutlich der erste symmetrische Multiprozessor.

Die Zeichkodierung nutzt ausschließlich 6-Bit Zeichen Kodierung [10, Seite III-3].

#### Prozessor.

Der Prozessor ist eine 36-Bit Akkumulator-Architektur [18, Seite 251] mit einem 36-Bit Akkumulator und einem zweiten 36-Bit Quotientenregister, welche sich für 72-Bit Fließkommazahlen auch als ein großes Register ansprechen lassen. Alle Befehle sind 36-Bit lang und können eine 18-Bit Adresse enthalten. Der eigentliche Befehlscode besteht aus 9 Bit,

Abbildung 1: Kleine Konfigurationen einer GE-635 [10, vgl. Seite I-4]

Abbildung 2: Große Konfigurationen der GE-635 [10, vgl. Seite I-4]

ermöglicht also 512 verschiedene Instruktionen. Alle Befehle, inklusive der Fließkommaoperationen sind fest verdrahtet (ohne Mikroprogramme) realisiert. Der Prozessor hat einen 72 Bit breiten Speicherbus und holt Befehle immer Paarweise. Es existieren ein privilegierter Modus für das Betriebssystem und ein unprivilegierter Modus, in welchem Benutzerprogramme laufen. Im unprivilegierten Modus werden alle Speicherzugriffe relativ zu einem BAR³ interpretiert und durch Limit-Register begrenzt, es gibt also auch hier schon virtuelle Adressen und Speicherschutz. Das Betriebssystem im privilegierten Modus hingegen hat immer direkten Speicherzugriff ohne Nutzung des BAR [10, Seite III-1].

### Speichermodul.

Das Speichermodul beinhaltet ein oder zwei Kernspeichermodule und die Technik, um mehrere Prozessoren und Ein-/Ausgabemodule anzubinden. Alle Zugriffe auf Ein-/Ausgabe finden immer durch Speicherzugriffe statt, darum ist es auch logisch, dass der Speicher das zentrale Element des Rechners ist und nicht irgendeine Form von Bus. Jedes Kernspeichermodul beinhaltet entweder 32768 oder 65536 Worte Speicher [10, Seite II-1].

# Ein-/Ausgabemodul.

Die Ein-/Ausgabemodule waren auch in sich wiederum modular aufgebaut und konnten Technik für verschiedenste Speicher und Ein-/Ausgabegeräte beinhalten. Magnetische Festplatten, Lochstreifen, Lochkarten, Magnetbänder, Fernschreiber und verschiedene Drucker lassen sich anschließen [10, Seite VII-1].

# 3.2.2 Geeignete Grundlage für Multics?

Für Multics wurden von Anfang an zwei grundlegende Anforderungen gestellt, zum einen sollte das System aus lose gekoppelten asynchronen Komponenten bestehen, da man schon mit einem hohen Negativeinfluss des Pagings und der Segmentierung auf die Leistung gerechnet hatte. Durch eine lose Koppelung sollte dieser Einfluss minimiert werden. Diese Anforderung erfüllte schon die GE-635 vollständig.

Die 2. wichtige Anforderung war Multiprozessorfähigkeit und die damit verbundene Skalierbarkeit einzelner Systeme. Auch diese Anforderung erfüllt bereits die GE-635, mit der Möglichkeit einen Rechner mit nur Teilweise geteiltem Speicher zu betreiben sogar über die für die GE-645 genutzte enge Kopplung hinaus. Beide Systeme unterstützen im UMA-Betrieb bis zu 4 Prozessoren.

Auch existiert bereits ein Adressraumschutz und das Konzept von 2 Privilegierungsebenen, welche für Multics wichtig waren. Der Adressraumschutz ist durch Eingrenzung mit Basisregister realisiert, einer zu dieser Zeit üblichen Technik. Allerdings wurde der Adressraumschutz, welcher auf der GE-635 lediglich durch Eingrenzung funktionierte, für die GE-645 vollständig ersetzt.

Das die GE-635 alle Zugriffe auf Ein- und Ausgabe auf Speicherzugriffe abbildet, passt auch sehr gut in das Konzept von Multics, in welchem alles konzeptionell auf Speicherzugriffe mit Segmentierung abgebildet werden sollte.

Auch existierten für die GE-635 bereits Fortran IV und COBOL-61 Übersetzer, es existierte also auch schon das Wissen, wie sich Übersetzer für diese Maschine konstruieren lassen. Rückblickend half dies der Entwicklung des PL/1

Übersetzers aber nicht, sondern kann nur als Machbarkeitsbeweis gesehen werden. Jedoch wurde die Unterstützung für Fortran und COBOL später auch auf der GE-645 für Anwendungsprogramme genutzt.

Zusammenfassend lässt sich also festhalten, dass die GE-635 eine sehr geeignete Grundlage für das geplante war und sicherlich nicht die schlechteste Wahl darstellte.

#### 3.2.3 6.36 Simulator

Auch wenn ich keine Details finden konnte, so sollte doch erwähnt werden, dass mit Hilfe des 6.36 Emulators auch auf einer GE-635 bereits Multics laufen sollte, mit einem hundertstel der erwarteten Geschwindigkeit einer echten GE-645, welche zu diesem Zeitpunkt noch GE-636 genannt werden sollte [14].

#### 4. GE-645

Die GE-645 ist die eigentliche Multics-Architektur. Im Folgenden werden die Aspekte betrachtet, welche sie von ihren Vorgängern unterscheiden und Multics spezifisch sind.

# 4.1 Unterschiede zur GE-635

Verglichen mit den 3 Grundelementen der GE-635, dem Prozessor, Speichermodul und Ein-/Ausgabekontroller, besteht eine GE-645 aus Prozessor, System-Steuerungs-Modul, System-Konfigurations-Konsole,  $\mathrm{GIOC}^4$  und erweitertem Speicher.

Das SCM<sup>5</sup> nimmt die Rolle des Speichermoduls ein, der Name zeigt jedoch schon, dass es deutlich mehr als nur Speicher ist. Zusätzlich ist durch die dynamische Rekonfigurierbarkeit die Konsole wichtiger geworden und wird darum nun als eine der Kernkomponenten aufgeführt. Außerdem völlig neu hinzugekommen ist das Konzept eines Erweiterungsspeichers für den Arbeitsspeicher.

Während Wort- und Adresslängen nicht konfigurierbare Eigenschaften der Hardware sind, ist die Länge eines Zeichens, im Gegensatz zur GE-635 konfigurierbar. Sie kann entweder 6 oder 9 Bit betragen. Diese Konfiguration lässt sich auch mischen, so dass ein Fernschreiberadapter 6 Bit Kodierung nutzt und ein anderer 9 Bit Kodierung [6, Seite 83].

Bei den möglichen Peripheriegeräten und Speichermedien gab es keine nennenswerten Änderungen.

### 4.1.1 Seitenverwalteter Speicher

Seitenverwaltung wurde mindestens auf einer Architektur vor der GE-645 realisiert, dem Atlas System[8] von 1961. Der Atlas nutzte einen seitenbasierten Speicher mit einer festen Seitengröße von 512 Worten und die Speicherverwaltung wurde mittels privilegierter Instruktionen vom Betriebssystem bereitgestellt. Dafür war auch bereits eine Seitenersetzungsstrategie, welche die Seitenverwaltung optimiert nötig, welche als "DRUM TRANSFER LEARNING program" bezeichnet wurde. Das Verfahren entsprach bereits damals  $\rm LRU^6$ . In der GE-645 wurde die Seitenverwaltung mit einer variablen Seitengröße von entweder 64 oder 1024 Worten realisiert. Die Größe einer Seite war in dem zu ihr gehörenden Segmentdeskriptor festgelegt. Alle Seiten eines Segments hatten somit die gleiche Größe, in unterschiedlichen

<sup>&</sup>lt;sup>3</sup>Base Address Register (Basis-Adress-Register)

<sup>&</sup>lt;sup>4</sup>Generalized Input Output Controller (Generalisierte Ein-/Ausgabe-Steuerung)

System Controller Module (System-Steuerungs-Modul)

<sup>&</sup>lt;sup>6</sup>Least Recently Used

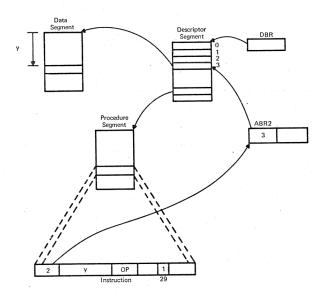

Abbildung 3: Normale Funktionsweise der Segmentierung mit ABR [6, Seite 24]

Segmenten konnten jedoch unterschiedlich große Seiten existieren [6, Seite 71]. Die Möglichkeit verschieden großer Segmente wurde von Multics nicht genutzt. Die Seitenersetzung wurde mittels eines "used-bit" Pseudo-LRU Algorithmus realisiert [1].

#### 4.1.2 Segmentierung

Wie auch das Konzept des Seiten-verwalteten Speichers, war auch die Segmentierung kein völlig neues Konzept, sondern existierte bereits vorher in mindestens einem anderen System, dem B5000[4]. Neu war jedoch, beide Konzepte zu kombinieren. Dies fand zeitgleich allerdings auch bei IBMs System 360 Projekt statt, ist also kein Alleinstellungsmerkmal[1].

Die Anforderung für Multics war, ein System zu konstruieren, welches mit einer großen Zahl von Segmenten gleichzeitig arbeiten konnte, da Segmente sehr intensiv und konsequent genutzt werden sollte.

So wie UNIX später "alles ist eine Datei" zum Prinzip machte, so war in Multics alles ein Segment. Geöffnete Dateien wurden als Segmente in den Speicher geblendet, dynamisches Linken mittels Segmenten realisiert. In den Konsequenten frühen Plänen sollte jede reine (pure) Bibliotheksfunktion ein eigenes Segment sein. Durch diese konsequente Nutzung musste auch die Hardware darauf ausgelegt sein, mit diesen Segmenten schnell arbeiten zu können.

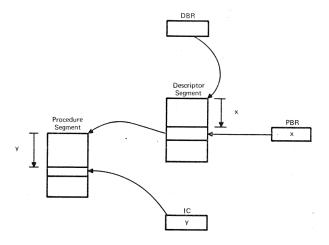

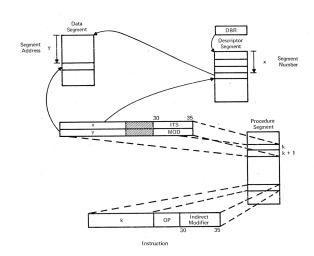

Die Segmentierung nutzt das DBR<sup>8</sup> als Zeiger auf die Speicherstelle, an welcher das Segment-Deskriptor-Segment liegt. Diese enthält für jedes Segment ein SDW<sup>9</sup>, welches wiederum die Speicheradresse des Segments, seine Größe, seinen Typ und Zugriffsrechte enthält. Veranschaulicht wird das in Abbildung 4.

Für die Auswahl der aktuell genutzten Segmente existie-

Abbildung 4: Auf Instruktionen wird DBR-relativ zugegriffen [6, Seite 25]

ren das PBR<sup>10</sup>, welches auf das aktuelle Prozedursegment zeigt und acht ABR welche sich entweder als Zeiger auf Datensegmente oder als Indizes innerhalb dieser Segmente nutzen lassen. Reguläre Datenzugriffe unter Verwendung der ABR zeigt Abbildung 3. Alle Segmentadressen sind 18 Bit und bilden mit den Segmentversatz einen Virtuellen 24 Bit Adressraum. Die Zugriffsrechte der Segmente Stehen hierarchisch über den für einzelne Seiten definierten Rechten. Seiten können also immer nur zusätzliche Einschränkungen erheben. Auch stellt die Hardware sicher, dass Daten sich nicht ausführen lassen und das Segment und Seitendeskriptoren in einem Deskriptorsegment liegen müssen. Auch existiert das Konzept von "Pure Functions", zustandslosen Funktionen, welche darum vollständig Schreibgeschützt sein können und welche in eigenen Segmenten liegen, in welche nur an den Beginn des Segments gesprungen werden kann [16].

Die das vermutlich bemerkenswerteste Element des Segmentierungskonzepts der GE-645 sind die ITS<sup>11</sup> und ITB<sup>12</sup> Speicherzugriffe. Diese Zugriffsmodi interpretieren zugegriffene Speicherstellen wiederum als Segmentnummer und Versatz innerhalb eines Segments (vergleiche Abbildung 5). Dies ist ein sehr komplexer Speicherzugriff und dabei können vielfache Fehler auftreten. Im Gegensatz zu dem GE-645 System Manual [6] von 1968 erwähnt The Multics System: An Examination of Its Structure [7, Seite 30] von 1972 explizit, dass diesen ITS und ITB Zeigern beliebig weit nach gelaufen wird. Es bleibt unklar, ob dies von Anfang an so implementiert war, oder es sich dabei um eine nachträgliche Modifikation handelt.

Es soll vorgekommen sein, dass ein einzelner Speicherzugriff eine 40 Sekunden anhaltende Folge von Speicherzugriffsfehler verursachte [13]. Der Unterschied der beiden Varianten ist, dass ITS Zugriffe direkt die Segmentnummer kodieren, während ITB Zugriffe noch eine Weitere Indirektion besitzen, da sie eine ABR Nummer enthalten, über die zugegriffen wird [6, Seite 23].

<sup>&</sup>lt;sup>8</sup>Descriptor Base Register

<sup>&</sup>lt;sup>9</sup>Segment Descriptor Word

<sup>&</sup>lt;sup>10</sup>Procedure Base Register (Prozedur-Basis-Register)

<sup>&</sup>lt;sup>11</sup>Indirect to Segment Modification (Indirekt relativ zur Anpassung des Segments)

<sup>&</sup>lt;sup>12</sup>Indirect to Base Modification (Indirekt relativ zur Anpassung der ABR-Basis)

Abbildung 5: Speicherzugriff mit Hilfe eines ITS Zugriffs [6, Seite 26]

# 4.1.3 Assoziativspeicher

Da durch Segmentierung und Seitenverwaltung Speicherzugriffe deutlich langsamer wurden, wurde ein Cache-Speicher, welcher die aufgelösten Hardwareadressen zwischenspeichert und so die Anzahl Speicherzugriffe verringert konstruiert. Dieser Speicher entspricht dem, was heute als TLB<sup>13</sup> bezeichnet wird und Teil jeder MMU<sup>14</sup> ist. Er fasste 16 Einträge und wurde Ebenfalls, wie die Seitenverwaltung mittels eines LRU-Algorithmus verwaltet, jedoch ist hier von einem Nutzungszähler, die Rede, was nahelegt, dass mehr als 1 Bit genutzt wurde. 16 Worte wirkt zwar nicht besonders groß, war nach Messungen [17] jedoch völlig ausreichend. Abbildung 6 zeigt die Messergebnisse, welche den nutzen des Assoziativspeichers belegen. Es wird sogar die Frage gestellt, ob 16 gegenüber 8 Einträgen den Mehrpreis wert sind, nachdem der Graph bereits merklich abflacht und der Gewinn eher klein ist.

# 4.1.4 Unterbrechungssteuerung

Die Unterbrechungsbehandlung erforderte auch Anpassungenungen bei der GE-645, besonders für Segmentierung und Seitenverwaltung. Die ITS und ITB Zugriffe können bei einem einzelnen Zugriff beliebig viele Seitenfehler auslösen, welche behandelt werden müssen, bevor dieser einzelne Befehl abgeschlossen ist. Somit ist es keine Option Unterbrechungen nur zwischen Befehlen auszuführen, sondern unpräzise Unterbrechungen sind nötig, welche zu exakten Punkten innerhalb einer einzelnen Instruktion behandelt werden. Da diese Unterbrechungen sich nicht verzögern lassen, haben sie auch die höchste Priorität, welche in der GE-645 faults genannt werden. Daneben existieren noch 2 weitere Klassen interrupts und low priority faults. Die beiden niederprioren Klassen lassen sich durch Bit 28 in der ausgeführten Instruktion unterdrücken, sofern der Prozessor sich im privilegierten Modus befinden. Im unprivilegierten Modus wird dieses Bit ignoriert, somit können Anwenderprogramme den Prozessor nicht monopolisieren. [6, Seite 29] Um vom Be-

Abbildung 6: Rechenleistung relativ zur Größe des Assoziativspeichers [17, Seite 240]

triebssystem ausgelöste Verklemmungen erkennen und beheben zu können, löst der Prozessor, wenn Unterbrechungen für mehr als 2 Millisekunden unterdrückt waren einen lockup fault [6, Seite 31] aus.

Überraschen mit Blick auf Unix und viele Nachfolgende System ist, dass die System-Uhr 52 Bit fasste und bei einer Auflösung von einer Mikrosekunde vom 1. Januar 1901, 0 Uhr aus 142 Jahre laufen kann, ohne über zulaufen. Damit könnte ein Multics-System jede Unix-Installation mit 32-Bit Systemzeit überdauern.[14]

Interrupts konnten sowohl durch Befehle ausgelöst werden, also auch von externen Quellen wie dem GIOC oder der System Clock.

### 4.1.5 Generalisierte Ein-/Ausgabesteuerung

Der GIOC unterschied sich nicht grundlegend von seinem Gegenstück in der GE-635. Das Konzept, dass eine modulare Einheit mit Hilfe von sogenannten "Adaptern" unterschiedliche Geräte anbinden kann blieb erhalten. Alle Zugriffe laufen über Single-Duplex Verbindungen ab, welche entweder Listen oder Daten-Kanäle sind. Über Listenkanäle sendet der Prozessor Befehle an den GIOC, welcher diese dann autonom ausführt. Die Befehle können nur einzelne Zugriffe sein, oder auch Blockübertragungen und verstreutes Einsammeln. Für diese Zeit eine wichtige Neuerung war, dass neben den Fernschreibern für die Interaktive Benutzung auch graphische Terminals mit Bildschirm unterstützt wurden. Graphisch bedeutet in diesem Kontext jedoch lediglich, dass der Cursor frei positionierbar war, alle Darstellung war Zeichen basiert.

Bemerkenswert an dieser Stelle ist, dass dabei auch schon der Speicherschutz beachtet wurde, man also davon sprechen könnte, das dieses System funktional über etwas wie eine

<sup>&</sup>lt;sup>13</sup>Translation Lookaside Buffer (Seitenübersetzungspuffer)

<sup>&</sup>lt;sup>14</sup>Memory Management Unit (Speicherverwaltungseinheit)

# 4.1.6 Erweiterter Speicher

Neu hinzukam eine zweite Kategorie von Trommelspeichern, eine Trommel mit starren Köpfen, welche als Auslagerungsspeicher für die Speicherseiten diente. Diese Trommel fasste 4 Millionen 36-Bit Worte und konnte bis zu 1024 Worte als Blocktransfer übertragen. Innerhalb von Multics wurde diese Trommel als *Librafile* bezeichnet, während das Systemhandbuch konsequent von *Extendet Memory* spricht [15]. Dieser Speicher war direkt an das Speichermodul gekoppelt und nicht über den GIOC.

### 4.1.7 Zugriffsschutz

Ein wichtiges Thema für ein System, welches Multitasking ermöglichen soll sind Zugriffsschutzmechanismen. Diese Mechanismen werden hier zusammengefasst, da sie sich mit verschiedenen Themen überlappen.

Der erste Teil des Zugriffsschutzes sind die 3 Prozessormodi. Neu gegenüber der GE-635 ist ein Absolut-Modus, welcher den virtuellen Speicher vollständig deaktiviert und es ermöglicht vollständig direkt abgebildet auf den Speicher zuzugreifen. Die anderen beiden Modi, Meister und Sklave nutzen beide die neuen Mechanismen des Speicherschutzes.

Einige privilegierte Befehle lassen sich, um die Isolation zwischen Benutzerprozessen sicherzustellen, nur im Absolut-Modus und im privilegierten Modus nutzen.

Das sind Befehle, mit welchen Ein-/Ausgabe konfiguriert wird, das verändern des DBR und das setzen der zeitgesteuerten Unterbrechung. Alle eigentlichen Eingaben und Ausgaben sind auf Speicherzugriffe abgebildet und somit nicht privilegiert, sie erfordern lediglich die entsprechenden Zugriffsrechte auf dem Speichersegment, auf welches das Gerät abgebildet wurde.

Die Segmente spielen eng in das Rechtekonzept hinein, da Segmente, welche Programmcode enthalten, auch entweder dem privilegierter oder dem unprivilegierten Modus zugeteilt sind, solange sie keine schreibgeschützten reinen Prozeduren sind. Da das Rechtesystem Zugriffsrechte auf Segmenten verwalten kann, besteht keine Notwendigkeit, Betriebssystem und Benutzerprogramme in verschiedenen Adressräumen laufen zu lassen, sonder das gesamte System konnte in einem Adressraum laufen.

### 4.1.8 System-Konfigurations-Konsole

Die SCC<sup>16</sup> speichert und stellt die Konfiguration des Systems allen anderen Komponenten bereit. Daneben bildet dieses Bauteil auch die für diese Zeit typische Bedienkonsole, von welcher aus ein Operateur den Rechner steuert.

Eines der vielleicht ungewöhnlichsten Konzepte, welches es in dieser Form heute auch selten gibt, ist die Möglichkeit ein GE-645 System im laufenden Betrieb umzukonfigurieren und sofern mehr als ein Prozessor und mehr als ein SCC vorhanden sind, auch aufzuteilen.

Dies Konfiguration des aktuell laufenden Systems befindet sich auf auf einer Lochkarte in der SCC und beinhaltet bis zu 473 Konfigurations-Bits. Die Konsistenz dieser Informationen muss von dem Bedienpersonal sichergestellt werden. Wenn mehr als ein SCC in dem System existiert, so existiert,

Abbildung 7: Ein teilbares GE-645 System mit zwei SCC

solange das System als ein Rechner betrieben wird trotzdem nur eine Lochkarte. Diese Steckt in der einzigen SCC welcher sich im "LOCAL" Modus befindet, während alle anderen SCCs ihre Konfiguration "REMOTE" von diesem beziehen.

Die Rekonfiguration muss notwendigerweise von Hand initiiert werden. Soll eine Installation geteilt werden, so wird diese Lochkarte durch eine neue, welche eine Konfiguration, die nur einen Teil des Gesamtsystems nutzt ersetzt und das System übernimmt diese Konfiguration. Anschließen kann der nur Freistehende Teil des Rechners von der zweiten SCC, welcher nun ebenfalls auf "LOCAL" gestellt wird, konfiguriert werden. Wichtig dabei ist, dass der zweite SCC hierarchisch unter dem ersten steht und nur Geräte nutzen kann, welche in der letzten Rekonfiguration frei geblieben sind. Ein Beispiel für eine mittel große GE-645 Installation mit zwei SCC, welche sich aufteilen lässt, zeigt Abbildung 7. Die Trennlinie soll eine die mögliche Unterteilung zeigen. Dieses kleine System lässt sich nur auf diese eine Art Teilen, da alle Notwendigen Komponenten jeweils nur einfach vorhanden sind.

Natürlich lässt sich das System nicht nur aufteilen, sondern auch wieder zusammenfügen. Laut dem GE-645 Handbuch [6, Seite 47] dauert eine solche Rekonfiguration 2,5 Sekunden.

Interessant an dieser Technik ist, dass sie ein Live-Update ermöglicht, indem ein System halbiert wird, angemeldete Nutzer bleiben auf einer Hälfte, das Betriebssystem der zweiten Hälfte wird aktualisiert und alle neuen Nutzer melden sich auf dem neuen System an. Sobald alle Nutzer auf der 1. Hälfte sich abgemeldet haben, lässt sich das System wieder auf den ganzen Rechner ausdehnen.

Auch wurde diese Technik genutzt um in der Nacht ein Testsystem zu haben, tagsüber aber die gesamte Installation als Produktivstem zu nutzen. Diese Technik ist ungewöhnlich aus heutiger Sicht, aber eigentlich nur deshalb, weil alle Anwendungsfelder heute von Virtualisierung abgedeckt werden.

### 5. WEITERE ENTWICKLUNG UND FAZIT

Aus Sicht der Rechnerarchitektur sind die beiden Nachfolgesysteme, auf welchen Multics ebenfalls lief wenig span-

<sup>&</sup>lt;sup>15</sup>Input Output Memory Management Unit (Ein-/Ausgabe-Speicherverwaltungseinheit)

<sup>&</sup>lt;sup>16</sup>Systems Configuration Console (System-Konfigurations-Konsole)

nend. Während der Entwicklung hatte Honeywell die Mainframe-Sparte von General Electrics übernommen. Honeywell betrieb weiter Modellpflege, aber die für Multics wichtigen Anpassungen waren in der GE-645 alle bereits enthalten.

# 5.1 Honeywell 6180 und DPS-8M

Es gab zwar viele Modernisierungen, das System aus Integrierten Schaltkreisen zu bauen, was die Geschwindigkeit steigerte, am Grundentwurf änderte sich aber nur sehr wenig. Der Prozessor behielt die 18-Bit Adressen, die 36-Bit Befehle, die wenigen Register. Der größte Unterschied ist wohl, dass schon mit der Honeywell 6180 8 Hardwareschutzringe existierten. Das ist zwar deutlich mehr als die 2 Ringe der GE-645, aber immer noch viel weniger als die 64 Ringe, welche Multics intern nutzte. Interessant ist, dass während frühere Systeme entweder Segmentierung und Seitenverwaltung oder Adressraumschutz durch Eingrenzung unterstützten. Dadurch konnte auf einer GE-645 zwar Multics ausgeführt werden, nicht jedoch General Electrics eigenes GECOS Betriebssystem. Die späteren Systeme beherrschten beide Modi, so dass auch die Multics Rechner in der Lage waren, GECOS auszuführen [12].

### 5.2 Fazit

Viele Konzepte der Architektur des GE-645 Rechners, welche für Multics in dieser Form zum ersten Mal in einem Rechner vereint wurden, existieren noch heute in sehr ähnlicher Form. Auch sind sogar die Begrifflichkeiten in den meisten Fällen, von dem Assoziativspeicher abgesehen, welcher heute als TLB bezeichnet wird, erhalten geblieben. Die Struktur von Segmentierung und Paging in einem 32-Bit x86 System ist strukturell eine vereinfachte Fassung dessen, was schon in den 1960er Jahren in der GE-645 realisiert wurde. Gerade die Konzepte des Speicherschutzes wirken sehr modern. Ein System welches jede Funktion in ihr eigenes Segment legt und darüber hinaus verhindert, dass an irgendeine andere Stelle als den eigentlichen Einsprungpunkt gesprungen wird, ermöglicht kein Return-Oriented-Programming [3] und Adressen ließen sich auf Ebene einzelner Funktionen randomisieren. Auch ist die Trennung der Schutz-Ringe sehr strickt und verhindert, dass GE-645 Sklavenprozeduren im Meistermodus laufen können oder umgekehrt. Auch grundlegende Konzepte der Entwicklungsarbeit, wie die Simulation eines Systems vor seiner Realisierung, haben bis heute Bestand.

### 6. Literatur

- A. Bensoussan, C.T. Clingen, R.C. Daley. The Multics Virtual Memory: Concepts and Design. Communications of the ACM, 15(5):[308-318], May 1972.

- J. Bellec. from GECOS to GCOS8. 2003.

http://www.feb-patrimoine.com/english/gecos\_to\_gcos8\_part\_1.htm [Online; abgerufen 11. November 2015].

- [3] E. Buchanan, R. Roemer, and S. Savage. Return-oriented programming: Exploits without code injection. Blackhat, 2008. http://cseweb.ucsd.edu/~hovav/talks/blackhat08.html [Online; abgerufen 13. November 2015].

- [4] M. Burroughs Corp., Detroit. The descriptor a definition of the b5000 information processing system. 1961.

- [5] Centre for Computing History. GE-635 System Manual Description. 2015.

http://www.computinghistory.org.uk/det/15671/ GE-635-System-Manual/ [Online; abgerufen 11.

November 2015].

- [6] G. Electrics. GE-645 system manual. 1968.

- [7] Elliott I. Organick. The Multics System: An Examination of Its Structure. The Massachusetts Institute of Technology, 1972.

- [8] T. K. et al. One level storage system. 1961.

- [9] General Electric. 600-Series Brochure.

- [10] General Electrics. GE-635 system manual. 1964.

- [11] E. L. Glaser, J. F. Couleur, and G. A. Oliver. System design of a computer for time sharing applications. Fall Joint Computer Conference, 1965.

- [12] Honeywell. DPS/LEVEL 68 and DPS 8M MULTICS PROCESSOR MANUAL.

- [13] John Gintell. Multics ACM Lecture Nov 16. 1989. https://www.youtube.com/watch?v=L8Bay04lCxs [Online; abgerufen 12. November 2015].

- [14] Multicians. Multicians/features. 2015. http://www.multicians.org/features.html [Online; abgerufen 12. November 2015].

- [15] Multicians. Multicians/glossary. 2015. http://www.multicians.org/mgl.html [Online; abgerufen 12. November 2015].

- [16] Multicians. Multicians/protection. 2015. http://www.multicians.org/protection.html [Online; abgerufen 12. November 2015].

- [17] M. D. Schroeder. Performance of the GE-645 associative memory while multics is in operation. Proceedings of the SIGOPS workshop on System performance evaluation, pages 227 – 245, 1971.

- [18] Walter Oberschelp, Gottfried Vossen. Computer architecture. Oldenbourg Verlag, 2006.

- [19] Wikipedia. Mistram. 2015. http://en.wikipedia.org/wiki/mistram [Online; abgerufen 12. November 2015].