# Betriebssysteme (BS)

## Zusammenfassung und Ausblick

Daniel Lohmann

Lehrstuhl für Informatik 4

Verteilte Systeme und Betriebssysteme

### Was wir gemacht haben

- VL 1: Einführung

- VL 2: Einstieg in die Betriebssystementwicklung

- VL 3: Unterbrechungen - Hardware

- VL 4: Unterbrechungen - Software

- VL 5: Unterbrechungen - Synchronisation

- VL 6: IA-32: Die 32-Bit-Intel-Architektur

- VL 7: Koroutinen und Programmfäden

- VL 8: Scheduling

- VL 9: Betriebssystem-Architekturen

- VL 10: Fadensynchronisation

- VL 11: Interprozesskommunikation

- VL 12: Bussysteme

- VL 13: Gerätetreiber

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

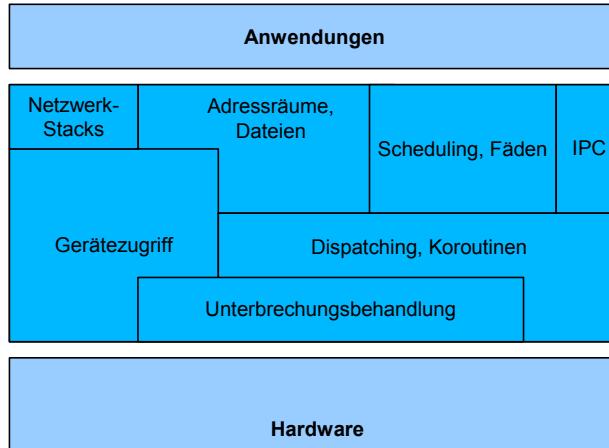

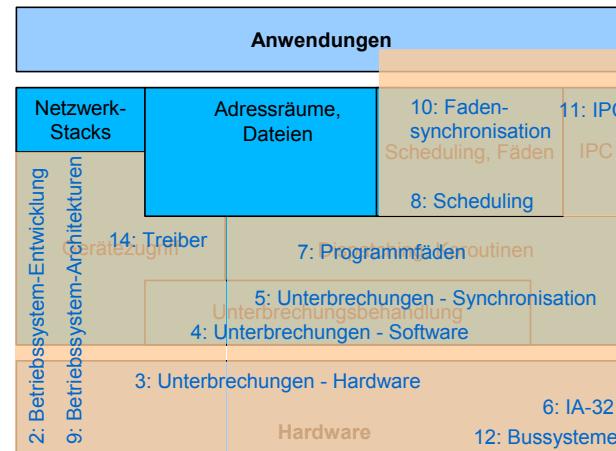

## Ausgangspunkt: Struktur eines BS

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

### Drei Inhaltliche Schwerpunkte

- VL 1: Einführung

- VL 2: Einstieg in die Betriebssystementwicklung

- VL 3: Unterbrechungen - Hardware**

- VL 4: Unterbrechungen - Software

- VL 5: Unterbrechungen - Synchronisation

- VL 6: IA-32: Die 32-Bit-Intel-Architektur**

- VL 7: Koroutinen und Programmfäden

- VL 8: Scheduling

- VL 9: Betriebssystem-Architekturen

- VL 10: Fadensynchronisation

- VL 11: Interprozesskommunikation

- VL 12: Bussysteme**

- VL 13: Gerätetreiber

**1. Ein Streifzug durch die Architektur des x86 PC**

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

## Drei Inhaltliche Schwerpunkte

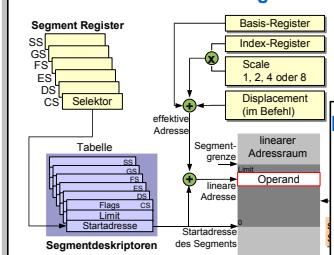

### IA-32: Protected Mode – Segmente

### 1. Ein Streifzug durch die Architektur des x86 PC

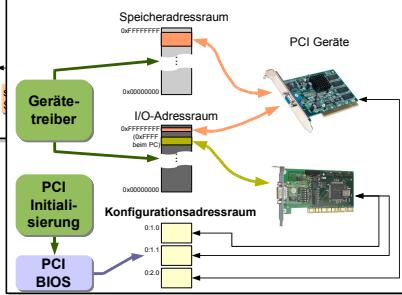

#### Interaktion mit PCI Geräten

## Drei Inhaltliche Schwerpunkte

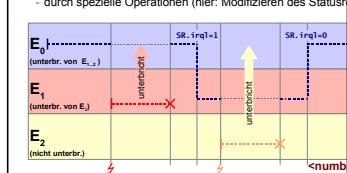

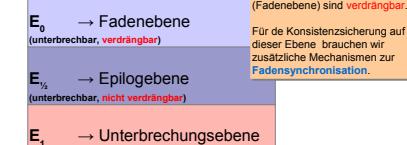

### Kontrollflussebenenmodell

- Verallgemeinerung für mehrere Unterbrechungsebenen:

- Kontrollflüsse auf  $E_i$  werden

1. **jederzeit unterbrochen** durch Kontrollflüsse von  $E_m$  (für  $m > i$ )

2. **nie unterbrochen** durch Kontrollflüsse von  $E_k$  (für  $k \leq i$ )

3. **sequentialisiert** mit weiteren Kontrollflüssen von  $E_i$

- Kontrollflüsse können die Ebene **wechseln**

- durch spezielle Operationen (hier: Modifizieren des Status)

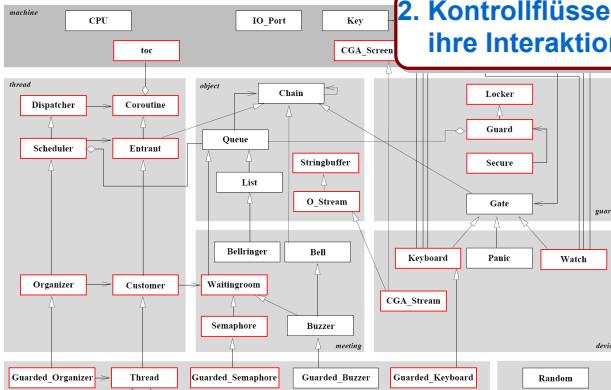

### 2. Kontrollflüsse und ihre Interaktionen

#### Erweitertes Kontrollflussebenenmodell

- Kontrollflüsse auf Ebene  $E_0$  sind

1. **jederzeit unterbrechbar** durch Kontrollflüsse von  $E_m$  (für  $m > i$ )

2. **nie unterbrechbar** durch Kontrollflüsse von  $E_k$  (für  $k \leq i$ )

3. **jederzeit verdrängbar** durch Kontrollflüsse von  $E_i$  (für  $i = 0$ )

## Drei Inhaltliche Schwerpunkte

### VL 1: Einführung

### VL 2: Einstieg in die Betriebssysteme

### 2. Kontrollflüsse und ihre Interaktionen

### VL 3: Unterbrechungen - Hardware

### VL 4: Unterbrechungen - Software

### VL 5: Unterbrechungen - Synchronisation

### VL 6: IA-32: Die 32-Bit-Intel-Architektur

### VL 7: Koroutinen und Programmfäden

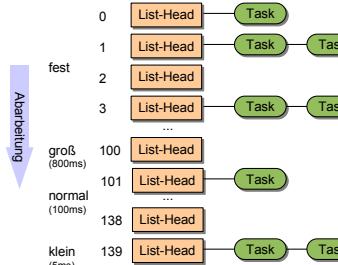

### VL 8: Scheduling

### VL 9: Betriebssystem-Architekturen

### VL 10: Fadensynchronisation

### VL 11: Interprozesskommunikation

### VL 12: Bussysteme

### VL 13: Gerätetreiber

## Drei Inhaltliche Schwerpunkte

### 2. Kontrollflüsse und ihre Interaktionen

## Drei Inhaltliche Schwerpunkte

- VL 1: Einführung

- VL 2: Einstieg in die Betriebe

- VL 3: Unterbrechungen - Hardware

- VL 4: Unterbrechungen - Software

- VL 5: Unterbrechungen - Synchronisation

- VL 6: IA-32: Die 32-Bit-Intel-Architektur

- VL 7: Koroutinen und Programmfäden

- VL 8: Scheduling**

- VL 9: Betriebssystem-Architekturen**

- VL 10: Fadensynchronisation

- VL 11: Interprozesskommunikation**

- VL 12: Bussysteme

- VL 13: Gerätetreiber**

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

9

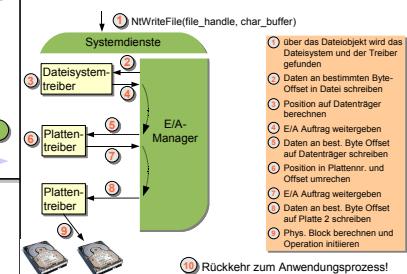

### 3. BS-Konzepte allgemein und in Windows / Linux

## Drei Inhaltliche Schwerpunkte

### Linux: Multi-Level Queues

Quantum Priorität (0 ist hoch, 139 niedrig)

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

### 3. BS-Konzepte allgemein und in Windows / Linux

### Windows – typischer E/A-Ablauf

Rückkehr zum Anwendungsprozess!

10

## Zusammen eine ganze Menge!

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

11

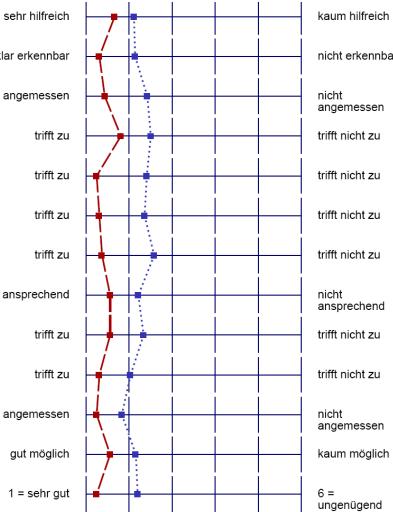

## Evaluationsergebnisse: VL-BS

### Globalindikator

1 2 3 4 5 6

mw=1.39

s=0.58

1 2 3 4 5 6

mw=1.52

s=0.76

1 2 3 4 5 6

mw=1.31

s=0.52

1 2 3 4 5 6

mw=1.48

s=0.64

1 2 3 4 5 6

mw=1.41

s=0.54

1 2 3 4 5 6

mw=1.25

s=0.45

### Gesamteindruck

n = 16 aus 32 (50%)

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

12

## Evaluationsergebnisse: VL-BS

4\_B) Die evtl. zusätzlich angebotenen Tutorien waren

## Ausblick: Vorlesung 15

### Kevin Klues, Stanford University

*The TinyOS Operating System:

Past, Present, and Future Directions*

- Nächsten Mittwoch zur gewohnten Zeit, **jedoch im H4**

- **Teilnahme ist Pflicht! :-)**

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

14

## Ausblick: Wie geht es danach weiter?

### Lehrveranstaltungen des LS4 im nächsten Semester

- Verteilte Systeme

- Echtzeitsysteme 2

- **Betriebssystemtechnik (OSE)**

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

15

## Eingebettete Systeme sind überall

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

16

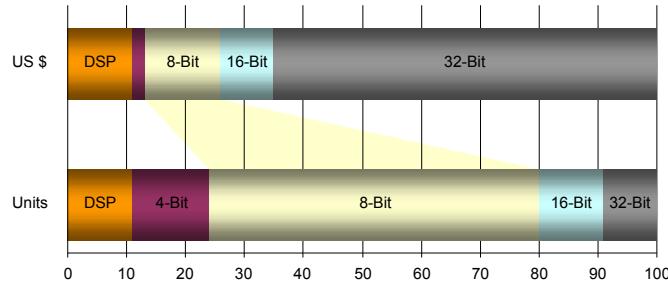

## Wo geht all das Silizium hin?

- eine Statistik aus dem Jahr 2002:

- von den etwa 8 Mrd. Prozessoren werden **mehr als 98%** im Bereich **eingebetteter Systeme** verwendet

- noch heute dominiert **8 Bit Technik**

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

17

## AVR ATmega – Eine typische Hardware-Produktlinie

μ-Controllerfamilie, basierend auf 8 Bit RISC-Core

- 16 general-purpose Register

- Havard-Architektur, getrennter Programm und Datenspeicher

- On-Board IO-Pins, Timer, AD-Wandler, Bussysteme, ...

Ein kleiner Ausschnitt aus den angebotenen Varianten:

| Bezeichnung | Prog.  | RAM  | IO  | Timer 8/16 | UART | PC | AD   | Preis |

|-------------|--------|------|-----|------------|------|----|------|-------|

| ATTINY11    | 1024   | 6    | 1/- | -          | -    | -  | -    | €0,31 |

| ATTINY13    | 1024   | 64   | 6   | 1/-        | -    | -  | 4*10 | €0,66 |

| AT90S2323   | 2048   | 128  | 3   | 1/-        | -    | -  | -    | €1,72 |

| ATMEGA8515  | 8192   | 512  | 35  | 1/1        | 1    | -  | -    | €2,04 |

| ATMEGA8535  | 8192   | 512  | 32  | 2/1        | 1    | 1  | -    | €2,67 |

| ATMEGA169   | 16384  | 1024 | 54  | 2/1        | 1    | 1  | 8*10 | €4,03 |

| ATMEGA64    | 65536  | 4096 | 53  | 2/2        | 2    | 1  | 8*10 | €5,60 |

| ATMEGA128   | 131072 | 4096 | 53  | 2/2        | 2    | 1  | 8*10 | €7,91 |

[Quelle: Digi-Key Produktkatalog, Sommer 2005]

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

18

## AVR ATmega – Eine typische Hardware-Produktlinie

μ-Controllerfamilie, basierend auf 8 Bit RISC-Core

- 16 general-purpose Register

- Havard-Architektur, getrennter Programm und Datenspeicher

- On-Board IO-Pins, Timer, AD-Wandler, Bussysteme, ...

Ein kleiner Ausschnitt aus den angebotenen Varianten:

| Bezeichnung | Prog.  | RAM  | IO  | Timer 8/16 | UART | PC | AD   | Preis |

|-------------|--------|------|-----|------------|------|----|------|-------|

| ATTINY11    | 1024   | 6    | 1/- | -          | -    | -  | -    | €0,31 |

| ATTINY13    | 1024   | 64   | 6   | 1/-        | -    | -  | 4*10 | €0,66 |

| AT90S2323   | 2048   | 128  | 3   | 1/-        | -    | -  | -    | €1,72 |

| ATMEGA8515  | 8192   | 512  | 35  | 1/1        | 1    | -  | -    | €2,04 |

| ATMEGA8535  | 8192   | 512  | 32  | 2/1        | 1    | 1  | -    | €2,67 |

| ATMEGA169   | 16384  | 1024 | 54  | 2/1        | 1    | 1  | 8*10 | €4,03 |

| ATMEGA64    | 65536  | 4096 | 53  | 2/2        | 2    | 1  | 8*10 | €5,60 |

| ATMEGA128   | 131072 | 4096 | 53  | 2/2        | 2    | 1  | 8*10 | €7,91 |

Systemsoftware muss

ähnlich gut skalieren!

[Quelle: Digi-Key Produktkatalog, Sommer 2005]

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

19

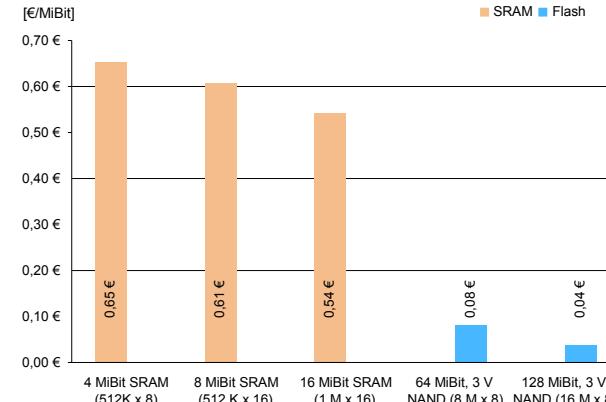

## Was macht die Hardware teuer?

- SRAM um den Faktor 10 teurer als Flash (ROM)

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

20

## Anforderungen sind vielfältig

### funktionale Anforderungen

voll-präemptiv,

Speicherschutz,

Prioritätsvererbung, ...

### nicht-funktionale Anforderungen

“schnell”

“energiesparend”

“verlässlich”

“deterministisch”

“klein”

“sicher”

### Eingebettetes Betriebssystem

ARM, PPC, TriCore, x86, HC12, AVR, ...

### Portabilitätsanforderungen

- Anforderungen sind hochgradig **anwendungsspezifisch**

- Vielzweckbetriebssysteme (wie im PC Bereich) versagen hier

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

21

## Eingebettete Betriebssysteme

..., C{51, 166, 251}, CMX RTOS, C-Smart/Raven, eCos, eRTOS, Embos, Ercos, Euros Plus, Hi Ross, Hynet-OS, LynxOS, MicroX/OS-II, Nucleus, OS-9, OSE, OSEK (Flex, Turbo, Plus), OSEKtime, Precise/MQX, Precise/RTCS, proOSEK, pSOS, PURE, PXROS, QNX, Realos, RTMOSxx, Real Time Architect, RTA, RTX{51, 166, 251}, RTXC, Softune, SSXS RTOS, ThreadX, TinyOS, VRTX, VxWorks, ...

Markt mit > 100 Systemen

> 50% Eigenentwicklungen

- „das Rad wird neu erfunden“

- auch die selben Fehler werden wiederholt

- oftmals bietet **ein** BS Hersteller **mehrere** Systeme an

- mit getrennter Code-Basis

- getrieben durch die speziellen Anforderungen seiner Kunden

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

22

## Konfigurierbare Betriebssysteme

- **Ansatz:** feingranulare, anwendungsspezifische, statische Konfigurierung

- Ersparnis von Ressourcen

- Abdeckung eines breiteren Anwendungsspektrums (=Marktes!)

- Wiederverwendung und damit höhere Produktivität

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

23

## Herausforderungen

### ... beim Bau konfigurierbarer Systemsoftware

- Beherrschung der Variantenvielfalt

- Analyse und Modellierung der Variabilität

- Minimierung der Modulabhängigkeiten, "Plug&Play"

- Systementwurf

- Wahl geeigneter Sprachmittel für die Programmierung

- Generizität und Wiederverwendbarkeit vs. Effizienz

- Werkzeugunterstützung

- Technik zur Konfigurierung

- ...

BS © 2006, 2007 Wolfgang Schröder-Preikschat, Olaf Spinczyk, Daniel Lohmann

24

## Herausforderungen

### ... beim Bau konfigurierbarer Systemsoftware

- Beherrschung der Variantenvielfalt

- Analyse und Modellierung der Variabilität

- Minimierung der Variabilität

- Software-Modellierung

- Variante auswählen

- Variante generieren

- Werkzeugunterstützung

- Technik zur Konfigurierung

- ...

Veranstaltung

**Operating System Engineering**

im Sommersemester 2008

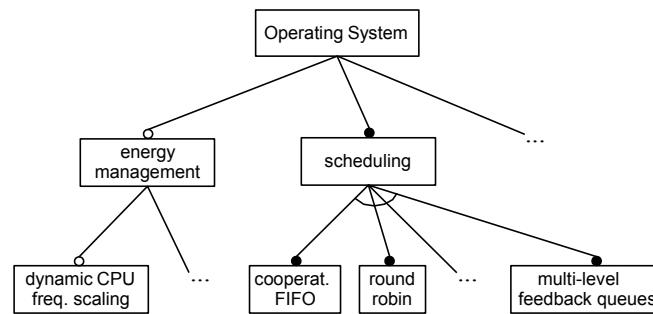

## Merkmallmodelle

### Merkmaldiagramm einer BS-Produktlinie

## Operating System Engineering (OSE)

### aka *Betriebssystemtechnik (BSE)*

- Vorlesung mit Übung (4 SWS, benoteter Schein)

- Inhaltliche Schwerpunkte: Vorlesung

- Methoden, Techniken, Werkzeuge für die Entwicklung von konfigurierbarer Systemsoftware

- Merkmalsmodellierung

- Aspektorientierte Programmierung (AOP)

- Inhaltliche Schwerpunkte: Übung

- Entwicklungsprojekt: Entwurf einer BS-Produktlinie für RCX / GBA

- Wie bekommt man Software **klein**?

- Wie bekommt man Software **konfigurierbar**?

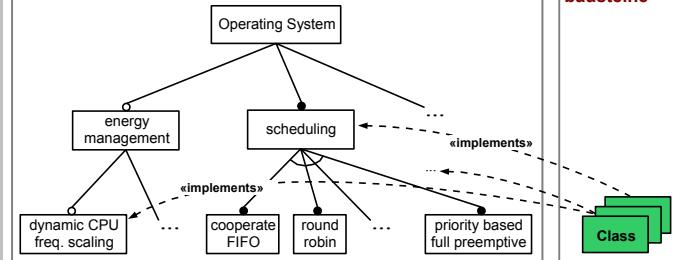

## Systembausteine

Idealfall: ein Merkmal wird durch **eine Klasse** implementiert

### Merkmaldiagramm

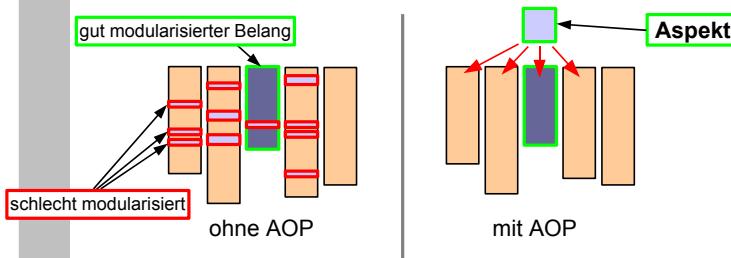

## Problem: Querschneidende Belange

... behindern Konfigurierung und Wiederverwendung

Multi-User Support

Synchronisation

Entwicklungsunterst.

```

MultiUserSupport.h

MultiUserSupport.cpp

Synchronization.h

Synchronization.cpp

Entwicklungsunterst.h

```

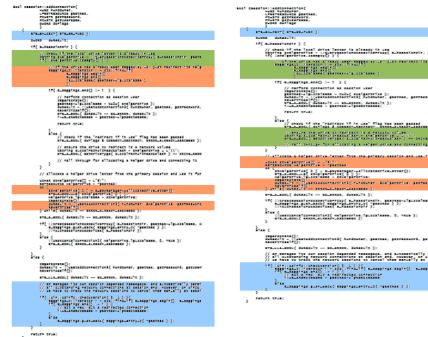

## Aspect-Oriented Programming

- ...erlaubt die modulare Implementierung querschneidender Belange

- Beispiele: Kontrollflussverfolgung, Synchronisation, Sicherheit, Pufferung, Fehlerbehandlung, Überprüfung von Kontrakten, ...

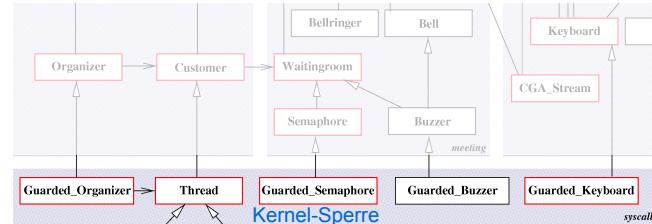

## Beispiel aus OO-Stubs: Kernel-Sperre

- Pro/Epilogmodell fordert:

- guard sperren, bevor der Kern betreten wird

- guard freigeben, nachdem der Kern verlassen wird

- Ansatz: Eigene Systemschnittstelle durch Ableitung

- Das ist gar nicht so toll! (Warum?)

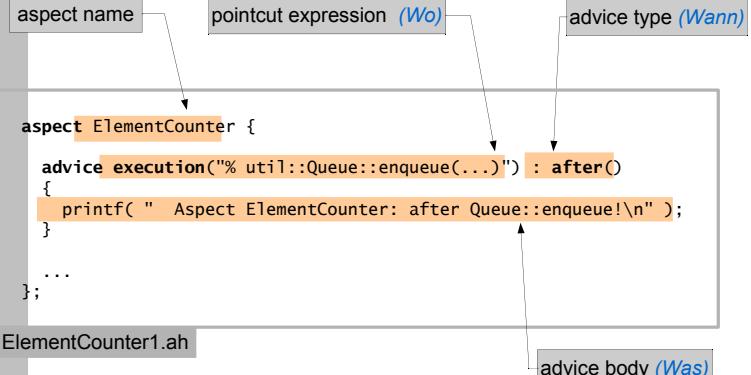

## AspectC++

```

#include "guard/guard.h"

extern Guard guard;

aspect KernelLock {

pointcut user() = "Application" || "Board" ...;

pointcut kernel() = "Buzzer" || "Keyboard" ...;

pointcut kernel_enter() = call(kernel())

&& within(user());

advice kernel_enter() : before() {

guard.enter();

}

advice kernel_enter() : after() {

guard.leave();

};

}

```

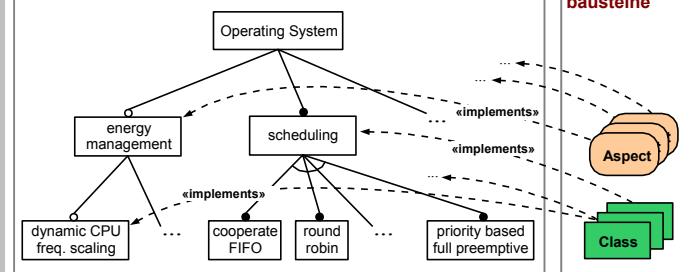

## Aspekte als Systembausteine

- Querschneidende Belange werden durch **Aspekte** implementiert

Merkmaldiagramm

Merkmale mit querschneidender Implementierung können nun direkt auf **ein** Modul abgebildet werden.

## Aspekte als Systembausteine

- Querschneidende Belange werden durch **Aspekte** implementiert

Merkmaldiagramm

Merkmale mit querschneidender Implementierung können nun direkt auf **ein** Modul abgebildet werden.