# Systemprogrammierung

Prozesssynchronisation: Befehlssatzebene

Wolfgang Schröder-Preikschat, Jürgen Kleinöder

Lehrstuhl Informatik 4

6. Dezember 2012

©wosch,jk (Lehrstuhl Informatik 4) Systemprogrammierung SP2 # WS 2012/13 C | X-4 Befehlssatzebene 2 Unterbrechungssteuerung Gliederung

- Unterbrechungssteuerung

- Prinzip

- Implementierung

- - Definition

- Implementierung

- Diskussion

- - Prinzip

- Elementaroperation

- Anwendung

- Diskussion

C | X-4 Befehlssatzebene

## Prozesssynchronisation auf der Befehlssatzebene

Alleinstellungsmerkmal dieser Abstraktionsebene sind allgemein die in der CPU manifestierten Fähigkeiten eines Rechensystems, hier:

- (a) in Bezug auf die Bereitstellung von Spezialbefehlen und

- (b) hinsichtlich der Semantik dieser Befehle zur Prozessverarbeitung

Techniken zur Synchronisation gleichzeitiger Prozesse können demzufolge nur auf sehr einfache, elementare Konzepte zurückgreifen

zu (a) die Möglichkeit, externe/interne Prozesse aussperren zu können

- Unterbrechungssperre

- Schlossvariable, Umlaufsperre

- zu (b) die Möglichkeit, kritische Abschnitte so ausformulieren zu können, dass gleichzeitige Prozesse nicht ausgesperrt werden

- nichtblockierende Synchroniation

©wosch,jk (Lehrstuhl Informatik 4)

SP2 # WS 2012/13

C | X-4 Befehlssatzeben

2.1 Prinzip

# Kontrolle asynchroner Programmunterbrechungen

Ansatz: asynchrone Programmunterbrechungen entweder verhindern oder tolerieren, und zwar durch Verzögerung der...

überlappenden Aktivität → pessimistisches Verfahren

• Spezialbefehle der { Ebene 2: cli, sti (x86) Ebene 3: sigprocmask (POSIX) }

überlappten Aktivität  $\mapsto$  optimistisches Verfahren

- durch Spezialbefehle und Programme der Ebene 2:

- CISC  $\hookrightarrow$  CAS (IBM 370, m68020+), CMPXCHG (i486+) RISC  $\hookrightarrow$  LL/SC (DEC Alpha, MIPS, PowerPC)

- ohne Spezialbefehle → BS/BST

"weich"

Unterbrechungen sperren: einfach — aber nicht immer zweckmäßig

• Faustregel: harte Synchronisation ist möglichst zu vermeiden

©wosch,jk (Lehrstuhl Informatik 4) Systemprogrammierung

SP2 # WS 2012/13

©wosch.ik (Lehrstuhl Informatik 4)

Systemprogrammierung

SP2 # WS 2012/13

C | X-4 Befehlssatzebene

2 Unterbrechungssteuerung

2.1 Prinzip

# Wiedersehen mit einem alten Problem: Überlapptes Zählen

```

int wheel = 0;

Plötzlich...

Schlecht...

void __attribute__ ((interrupt))

main () {

niam () {

for (;;)

wheel++;

printf("%u\n", wheel++);

```

#### Wettlaufsituation

- kritischer Abschnitt: ++

- Wettlaufgefahr vorbeugen

- ELOP int fai(int\*)

# Besser... main () { for (;;) printf("%u\n", fai(&wheel));

• unteilbares Zählen konstruktiv und problemadäguat sicherstellen

©wosch,jk (Lehrstuhl Informatik 4) Systemprogrammierung SP2 # WS 2012/13

C | X-4 Befehlssatzebene

2 Unterbrechungssteuerung

2.2 Implementierung

## Unterbrechungssperre: x86

```

typedef unsigned short irq_t; // flags register placeholder

void irg_block();

// disable interrupts at CPU

void irq_admit();

// enable interrupts at CPU

irq_t irq_avert();

// save CPU interrupt level then block

void irq_treva(irq_t);

// restore saved CPU interrupt level

void irq_block() {

void irq_admit() {

asm volatile("cli");

asm volatile("sti");

irq_t irq_avert() {

void irq_treva(irq_t flags) {

irq_t flags;

asm volatile(

asm volatile(

"push %0; popf"

"pushf; pop %0; cli"

: : "g" (flags));

: "=g" (flags));

return flags;

```

```

C | X-4 Befehlssatzebene

2 Unterbrechungssteuerung

```

# Verhinderung vs. Tolerierung von *Interrupts*

```

Verhinderung

Tolerierung

int fai (int *ref) {

int fai (int *ref) {

int aux:

int aux = 1:

asm volatile ("cli");

asm volatile ("xaddl %0,%1"

aux = (*ref)++;

: "=g" (aux), "=m" (*ref)

asm volatile ("sti");

: "0" (aux), "m" (*ref));

return aux;

return aux;

}

```

- Komplexbefehl der Ebene 3

- privilegierte Befehle cli/sti

- Elementaroperation des BS

- Komplexbefehl der Ebene 2

- unprivilegierter Befehl xadd

- Elementaroperation der CPU

## Beachte: Multiprozessorbetrieb

• die Befehle haben nur lokale Signifikanz für "ihren" Prozessor(kern)

©wosch,jk (Lehrstuhl Informatik 4)

Systemprogrammierung

SP2 # WS 2012/13 6 / 34

C | X-4 Befehlssatzebene

2 Unterbrechungssteuerung

2.2 Implementierung

## Schutz kritischer Abschnitte durch Unterbrechungssperre

```

solo-Optionen: Unterbrechungssperre

typedef irq_t solo_t;

```

```

#define CS_ENTER(solo) irq_block()

#define CS_LEAVE(solo) irq_admit()

```

- #define CS\_ENTER(solo) \*solo = irq\_avert() #define CS\_LEAVE(solo) irq\_treva(\*solo)

- für unverschachtelte KA

- ohne Zustandssicherung

- für verschachtelte KA

- mit Zustandssicherung

## Beachte: Unabhängige gleichzeitige Prozesse

• werden unnötig zurückgehalten, obwohl sie den KA nicht durchlaufen

### Beachte: Unterbrechungsverzögerung

- die größte WCET a aller durch Unterbrechungssperre gesicherten KA

- erhöhtes Risiko des Verlusts von Unterbrechungsanforderungen

<sup>a</sup>Abk. für (engl.) worst case execution time.

7 / 34

C | X-4 Befehlssatzebene

3 Schlossvariable

# Gliederung

- - Prinzip

- Implementierung

- Schlossvariable

- Definition

- Implementierung

- Diskussion

- - Prinzip

- Elementaroperation

- Anwendung

- Diskussion

©wosch,jk (Lehrstuhl Informatik 4)

Systemprogrammierung

SP2 # WS 2012/13

Systemprogrammierung

SP2 # WS 2012/13

C | X-4 Befehlssatzebene

3 Schlossvariable

3.2 Implementierung

# Schlossalgorithmus: Prinzip — mit Problem(en)

```

typedef struct lock {

volatile bool busy:

// status of critical section

// optional stuff needed for other variants

} lock_t;

```

### Wettlaufgefahr

```

void lv_acquire (lock_t *lock) {

while (lock->busy);

lock->busy = true;

```

```

void lv_release (lock_t *lock) {

lock->busy = false;

}

```

- die Phase vom Verlassen der Kopfschleife bis zum Setzen der Schlossvariablen ist kritisch

- gleichzeitige Prozesse können das Schloss geöffnet vorfinden, dann jeweils schließen und gemeinsam den kritischen Abschnitt belegen

### Abprüfen und setzen (engl. test and set, TAS) der Schloßvariablen

• muss als **Elementaroperation** und wirklich atomar ausgelegt sein

C | X-4 Befehlssatzebene

3 Schlossvariable

3.1 Definition

# Schlossvariable (engl. lock variable)

**Datentyp**, der zwei grundlegende Operationen definiert:

```

acquire (auch: lock) ⊨ Eintrittsprotokoll

```

- verzögert einen Prozess, bis das zugehörige Schloss offen ist

- bei geöffnetem Schloss fährt der Prozess unverzögert fort

- verschließt das Schloss ("von innen"), wenn es offen ist

release (auch: *unlock*) ⊨ Austrittsprotokoll

• öffnet ein Schloss, ohne den öffnenden Prozess zu verzögern

Implementierungen dieses Konzepts werden auch als Schlossalgorithmen (engl. lock algorithms) bezeichnet

©wosch,jk (Lehrstuhl Informatik 4)

C | X-4 Befehlssatzeben

3 Schlossvariable

3.2 Implementierung

## Schlossvariable atomar abprüfen und setzen

```

Kritischer Abschnitt: solo t

int tas(lock_t *lock) {

bool busy;

CS_ENTER(&lock->gate);

busy = lock->busy;

lock->busy = true;

CS_LEAVE(&lock->gate);

return busy;

```

lock\_t mit solo-Option:

- Verdrängungssperre *oder*

- Unterbrechungssperre

untauglich f

ür Multiprozessoren

Elementaroperation: x86

```

int tas(volatile bool *lock) {

bool busy:

busy = true;

asm volatile("lock xchgb %0, %1"

: "=q" (busy), "=m" (*lock)

: "0" (busy));

return busy;

```

• "read-modify-write" lock

atomarer Buszyklus

Operandenaustausch

tauglich für Multiprozessoren

xchgb

C | X-4 Befehlssatzebene 3.2 Implementierung

# Umlaufsperre (engl. spin lock)

```

..Drehschloss"

void lv_acquire (lock_t *lock) {

while (TAS(lock));

```

TAS kommt in zwei Varianten (S. 12):

- (a) int tas(lock\_t \*)

- (b) int tas(volatile bool \*)

## Gefahr von Leistungsabfall

- pausenloses Durchlaufen der Schleife allein nur mit TAS:

- (a) erhöht das Risiko, Anforderungen von Programmunterbrechungen oder Prozessverdrängungen zu verpassen

- die Unterbrechungs- bzw. Verdrängungssperre ist fast nur noch gesetzt

- (b) hindert andere Prozessoren am Buszugang bzw. sorgt für eine überaus hohe Last im Kohärenzprotokoll des Zwischenspeichers

- der Prozessor führt fast nur noch "read-modify-write"-Zyklen durch

- das Problem verschärft sich massiv, wenn (viele) gleichzeitige Prozesse den Wettstreit (engl. contention) um das "Drehschloss" aufnehmen

©wosch,jk (Lehrstuhl Informatik 4)

C | X-4 Befehlssatzebene

Systemprogrammierung

SP2 # WS 2012/13

3.3 Diskussion

C | X-4 Befehlssatzebene

3 Schlossvariable

SP2 # WS 2012/13 14 / 34

## Aktives Warten (engl. busy waiting)

3 Schlossvariable

Unzulänglichkeit der Schlossalgorithmen: der aktiv wartende Prozess. . .

- kann keine Änderung der Bedingung herbeiführen, auf die er wartet

- behindert andere Prozesse, die sinnvolle Arbeit leisten könnten

- schadet damit letztlich auch sich selbst

Je länger der Prozess den Prozessor für sich behält, umso länger muss er darauf warten, dass andere Prozesse die Bedingung erfüllen, auf die er selbst wartet.

- in den meisten Fällen sind Effizienzeinbußen in Kauf zu nehmen

- es sei denn, jeder Prozess hat seinen eigenen realen Prozessor(kern)

### Allgemein ein nur bedingt effektives Verfahren

notwendige Bedingung

- kurze Laufzeit des zu schützenden KA

- hinreichende Bedingung

- CPU-Abgabe nach gescheitertem Versuch bei gemeinsam benutzten Prozessor(kern)

# Sensitive Umlaufsperre

### Nichtinvasives Warten

C | X-4 Befehlssatzebene

```

void lv_acquire (lock_t *lock) {

while (lock->busy);

} while (TAS(lock));

```

#### Zurücktretendes Warten

```

void lv_acquire(lock_t *lock) {

while (true) {

while (lock->busy);

if (!TAS(lock)) break;

lv_backoff(lock);

}

}

```

• nur lesender Zugriff beim Warten

3.2 Implementierung

- Zwischenspeicherzeile gemeinsam benutzbar (MESI, [4])

- einmal "read-modify-write" (TAS)

- beruhigend für den Busverkehr

Eigenschaften wie zuvor, zusätzlich:

- Wettstreit (engl. contention) aus dem Wege gehend

- zusätzliche Wartezeit ("back-off") nach gescheitertem TAS

- prozessspezifisch, ansteigend

## Exponentielles Zurücktreten (engl. exponential back-off)

• beschränkte Wartezeitverdopplung mit jedem gescheitertem Versuch Systemprogrammierung

©wosch,jk (Lehrstuhl Informatik 4)

3.3 Diskussion

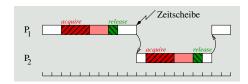

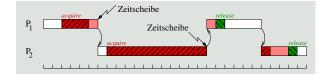

# Aktives Warten ohne Prozessorabgabe

"Spin locking considered harmful"

|       | $T_s$ | $T_q$ | $T_q/T_s$ |

|-------|-------|-------|-----------|

| $P_1$ | 12    | 20    | 1.67      |

| $P_2$ | 8     | 8     | 1.0       |

|       | $T_s$ | $T_q$ | $T_q/T_s$ |

|-------|-------|-------|-----------|

| $P_1$ | 12    | 24    | 2.0       |

| $P_2$ | 17    | 23    | 1.35      |

### Verbesserung: Prozessorabgabe in der Warteschleife (vgl. S. 34)

laufend → bereit

in Laufbereitschaft bleiben laufend → blockiert schlafend die Schlossfreigabe erwarten ps\_forgo

ps\_sleep

C | X-4 Befehlssatzebene

4 Nichtblockierende Synchronisation

## Gliederung

- - Prinzip

- Implementierung

- Schlossvariable

- Definition

- Implementierung

- Diskussion

- Nichtblockierende Synchronisation

- Prinzip

- Elementaroperation

- Anwendung

- Diskussion

©wosch,jk (Lehrstuhl Informatik 4)

Systemprogrammierung

SP2 # WS 2012/13

SP2 # WS 2012/13

C | X-4 Befehlssatzebene

4 Nichtblockierende Synchronisation

## Optimistisches Verfahren der Synchronisation

Nebenläufigkeit unterstützen, nicht einschränken wie beim wechselseitigen Ausschluss

Koordinierung sich einander ggf. überlappender Aktivitäten, ohne dabei gleichzeitige Prozesse auszuschließen

- toleriert (pseudo-) parallele Programmausführungen

- parallel

- Multiprozessor, wirkliche Parallelität

- Uniprozessor, Parallelität durch Unterbrechungen pseudoparallel

- die Verfahren greifen auf nichtprivilegierte Befehle der ISA zurück

- TAS, FAA, CAS bzw. CMPXCHG RISC LL/SC

- d.h., sie funktionieren im Benutzer- wie auch im Systemmodus

#### **Beachte**

- kein wechselseitiger Ausschluss ⇒ Verklemmungsvorbeugung

- die benutzten Befehle müssen "echte" Elementaroperationen

C | X-4 Befehlssatzebene

4 Nichtblockierende Synchronisation

# Blockierende Synchronisation "considered harmful"

Probleme von Schlossvariablen. Semaphoren und Monitoren

Leistung (engl. performance) insbesondere in SMP-Systemen [1]

• "spin locking" reduziert ggf. massiv Busbandbreite

Robustheit (engl. robustness) "single point of failure"

ein im kritischen Abschnitt scheiternder Prozess kann schlimmstenfalls das ganze System lahm legen

Einplanung (engl. scheduling) wird behindert bzw. nicht durchgesetzt

- un- bzw. weniger wichtige Prozesse können wichtige Prozesse "ausbremsen" bzw. scheitern lassen

- Prioritätsverletzung, Prioritätsumkehr [3]

- Mars Pathfinder [5, 2]

Verklemmung (engl. deadlock) einiger oder sogar aller Prozesse

©wosch,jk (Lehrstuhl Informatik 4)

C | X-4 Befehlssatzeben

4 Nichtblockierende Synchronisation

4.2 Prinzip

# Muster nichtblockierender Synchronisation (NBS)

```

NBS_mit_CAS ( ) {

do {

ziehe lokale Kopie des Inhalts der Adresse einer globalen Variablen;

verwende die Kopie, um einen neuen lokalen Wert zu berechnen;

versuche CAS: sichere den lokalen Wert an die Adresse, wenn ihr

Inhalt immer noch mit dem Wert der lokalen Kopie identisch ist;

} while (CAS_scheitert);

```

pros

- Tolerierung beliebiger Überlappungsmuster

- transparent für die Einplanung: keine Prioritätsumkehr

- Verklemmungsvorbeugung: kein wechselseitiger Ausschluss

- Robustheit: keine hängenden Sperren bei Programmabbrüchen

cons

- Wiederverwendung sequentieller Altsoftware unmöglich

- Gefahr von Verhungerung (engl. starvation) in simplen Lösungen

- Entwicklung nebenläufiger Varianten im Regelfall nicht trivial

©wosch,jk (Lehrstuhl Informatik 4)

Systemprogrammierung

SP2 # WS 2012/13

©wosch.ik (Lehrstuhl Informatik 4)

Systemprogrammierung

```

int cas(word_t *ref, word_t exp, word_t val) {

// assume bus resp. interrupt lock

solo_t gate;

bool done;

CS_ENTER(&gate);

if (done = (*ref == exp)) *ref = val;

CS_LEAVE(&gate);

return done:

```

- die Adresse des atomar, bedingt zu ändernden Speicherworts ref

- der unter der Adresse ref erwartete alte Wert exp

- der unter der Adresse ref zu speichernde neue Wert val

- die Speicherung erfolgt nur, wenn der unter ref gespeicherte Wert dem erwarteten Wert exp gleicht

- lag Gleichheit vor, liefert die Funktion true, anderenfalls false

©wosch,jk (Lehrstuhl Informatik 4)

Systemprogrammierung

SP2 # WS 2012/13

SP2 # WS 2012/13

SP2 # WS 2012/13 22 / 34

C | X-4 Befehlssatzebene

4 Nichtblockierende Synchronisation

4.4 Anwendung

# Sperrfreie (engl. lock-free) Wartestapelmanipulation

LCFS (Abk. für engl. last come, first served)

```

Aufnahme in die Liste...

void lf_push(chain_t *head, chain_t *item) {

do item->link = head->link:

// is elected head

while (!CAS(&head->link, item->link, item)); // try push item

}

```

```

Entnahme aus der Liste...

chain_t *lf_pull(chain_t *head) {

chain_t *item;

do if ((item = head->link) == 0) break:

// access head

while (!CAS(&head->link, item, item->link)); // try pull item

return item;

```

```

cas((word_t*)r, (word_t)e, (word_t)v)

#define CAS(r,e,v)

```

C | X-4 Befehlssatzebene

4.3 Elementaroperation

# Bedingte Wertzuweisung: CAS als Spezialbefehl (x86)

4 Nichtblockierende Synchronisation

```

ZF = (eax == *ref) ? (*ref = val, true) : (eax = *ref, false)

int cas(word_t *ref, word_t exp, word_t val) {

// "sete" writes to low byte of operand

unsigned char done;

asm volatile(

"lock\n\t"

// next comes atomic read-modify-write

"cmpxchgl %2,%1\n\t" // conditional exchange of operands

"sete %0"

// transfer value of zero flag (ZF bit)

: "=q" (done), "=m" (*ref)

: "r" (val), "m" (*ref), "a" (exp)

: "memory");

return done;

```

setzt die Bussperre f

ür den nachfolgenden Befehl

• zwingend für Multi(kern)prozessorsysteme, optional sonst

cmpxchgl

• compare & exchange:  $ZF = true \rightarrow Speicherung erfolgt$

• definiert Variable done mit dem Wert des ZF-Bits

©wosch,jk (Lehrstuhl Informatik 4)

Systemprogrammierung

C | X-4 Befehlssatzebene

4 Nichtblockierende Synchronisation

4.4 Anwendung

## Problem ABA

Transaktion gelingt trotz zwischenzeitlicher Änderungen

Phänomen der nichtblockierenden Synchronisation auf Basis eines CAS, d.h., einer ELOP, die inhaltsbasiert arbeitet<sup>1</sup>

- $\bullet$  angenommen zwei Fäden,  $F_1$  und  $F_2$ , stehen im Wettstreit um eine gemeinsame Variable V

- liest den Wert A von V, speichert diesen als Kopie, wird dann allerdings vor dem CAS<sub>V</sub> für unbestimmte Zeit verzögert

- durchläuft dieselbe Sequenz, schafft jedoch mittels CAS<sub>V</sub> den Wert B an V zuzuweisen

- anschließend wird (in einem weiteren Durchlauf dieser Sequenz) wieder der ursprüngliche Wert A an V zugewiesen

- setzt seine Ausführung mit CAS<sub>V</sub> fort, erkennt, dass V den Wert A seiner Kopie speichert und überschreibt V

- im Ergebnis kann dieses Überlappungsmuster dazu führen, dass  $F_1$ mittels  $CAS_V$  einen falschen Wert nach V transferiert

Systemprogrammierung

<sup>&</sup>lt;sup>1</sup>Bei Adressreservierung wie z.B. mit LL/SC besteht dieses Problem nicht.

## Problem ABA: Wartestapel mit Wettlaufsituation

Ausgangszustand der (LCFS) Liste:  $head \diamondsuit A \diamondsuit B \diamondsuit C$ , head ist  $ref_{CAS}$ :

|    |                  |      | CAS  | -Param |     |                                     |

|----|------------------|------|------|--------|-----|-------------------------------------|

|    | M                | Op.  | *ref | exp    | val | Liste                               |

| 1. | $F_1$            | pu// | Α    | Α      | В   | unverändert                         |

| 2. | $F_2$            | pull | Α    | Α      | В   | ref \$ B \$ C                       |

| 3. | $F_2$            | pull | В    | В      | C   | ref ⇔ C                             |

| 4. | $F_2$            | push | C    | С      | Α   | $ref \diamondsuit A \diamondsuit C$ |

| 5. | $\overline{F_1}$ | pull | Α    | Α      | В   | ref \$B\$⊕                          |

- 1. F<sub>1</sub> wird im pull vor CAS unterbrochen, behält lokalen Zustand bei

- 2.-4.  $F_2$  führt die Operationen komplett aus, aktualisiert die Liste

- 5. F<sub>1</sub> beendet pull mit dem zum Zeitpunkt 1. gültigen lokalen Zustand

©wosch,jk (Lehrstuhl Informatik 4)

Systemprogrammierung

SP2 # WS 2012/13

SP2 # WS 2012/13

28 / 34

C | X-4 Befehlssatzebene

4 Nichtblockierende Synchronisation

## Generationszähler "considered harmful"?

## Abhilfe (engl. workaround) zum ABA-Problem → Bedingte Lösung

- die Effektivität des Lösungsansatzes steht und fällt mit dem für den Generationszähler definierten endlichen Wertebereich

- dessen Auslegung letztlich vom jeweiligen Anwendungsfall abhängt

- Überlappungsmuster gleichzeitiger Prozesse haben Einfluss auf den für den Generationszähler zur Verfügung zu stellenden Wertebereich

- bestimmt durch Zusammenspiel und Anzahl der wettstreitigen Fäden

- ein Bit kann reichen, ebenso, wie ein unsigned int zu klein sein kann

- diese, dem jeweiligen Anwendungsfall zu entnehmenden Muster zu entdecken, ist zumeist schwer und nicht selten unmöglich

**Vorbeugung** (engl. *prevention*) muss zuerst kommen — sofern machbar:

- beliebige Überlappungsmuster konstruktiv (Entwurf) ausschließen

- oder auf Adressreservierungsverfahren der Hardware zurückgreifen

- unterstützt nicht jede Hardware, ist nur typisch für RISC

- z.B. ELOP-Paar load linked, store conditional (LL/SC) verwenden

## Kritische Variable mittels "Zeitstempel" absichern

Abhilfe besteht darin, den umstrittenen Zeiger (nämlich item) um einen problemspezifischen Generationszähler zu erweitern

#### Etikettieren

C | X-4 Befehlssatzebene

- Zeiger mit einem "Anhänger" (engl. tag) versehen

- Ausrichtung (engl. alignment) ausnutzen, z.B.:

$$sizeof(chain_t) \sim 4 = 2^2 \Rightarrow n = 2$$

$\Rightarrow chain_t * ist Vielfaches von 4$

$\Rightarrow chain_t *_{Bits[0:1]} immer 0$

• Platzhalter für *n*-Bit Marke/Zähler in jedem Zeiger

#### DCAS

- Abk. für (engl.) double compare and swap

- Marke/Zähler als elementaren Datentyp auslegen

- unsigned int hat Wertebereich von z.B.  $[0, 2^{32} 1]$

- zwei Maschinenworte (Zeiger, Marke/Zähler) ändern

- push bzw. pull verändern sodann den Zeigerwert um eine Generation

©wosch,jk (Lehrstuhl Informatik 4)

Systemprogrammierung

SP2 # WS 2012/13

4 Nichtblockierende Synchronisation

4.5 Diskussion

# Wiederholungsversuche — Aktives Warten?

Scheitern der etwa durch CAS<sup>2</sup> abzuschließenden Transaktion zieht die Wiederholung des kompletten Vorbereitungsvorgangs nach sich

- je höher der Grad an Wettstreitigkeit unter gleichzeitigen Prozessen, umso höher die Wahrscheinlichkeit, dass CAS scheitert

- ein zur Umlaufsperre sehr ähnliches Problem ergibt sich, das jedoch durch sensitive Techniken gleicher Art lösbar ist (vgl. S. 13-14)

- Häufigkeit von "read-modify-write"-Zyklen pro Durchlauf minimieren

- prozessspezifisches Zurücktreten vom erneuten Transaktionsversuch

- variable Wartezeiten, um Konflikte bei Wiederholungen zu vermeiden

### Unterschied zur Umlaufsperre

- gleichzeitige Prozesse müssen nicht untätig darauf warten, dass ein kritischer Abschnitt entsperrt wird und somit frei ist

- im Gegensatz zur Umlaufsperre kommen sie während ihrer Wartezeit mit ihren (lokalen) Berechnungen voran

<sup>2</sup>Für LL/SC-artige Elementaroperationen gilt dies ebenfalls.

C | X-4 Befehlssatzebene 5 Zusammenfassung

# Gliederung

- Prinzip

- Implementierung

- Schlossvariable

- Definition

- Implementierung

- Diskussion

- Nichtblockierende Synchronisation

- Prinzip

- Elementaroperation

- Anwendung

- Diskussion

- Zusammenfassung

©wosch,jk (Lehrstuhl Informatik 4) Systemprogrammierung SP2 # WS 2012/13 29 / 34

C | X-4 Befehlssatzebene

5 Zusammenfassung

5.1 Bibliographie

## Literaturverzeichnis

[1] Bryant, R.; Chang, H.-Y.; Rosenburg, B. S.: Experience Developing the RP3 Operating System. In: Computing Systems 4 (1991), Nr. 3, S. 183-216

[2] JONES, M. B.:

What really happened on Mars? http://www.research.microsoft.com/~mbj/Mars\_Pathfinder/Mars\_Pathfinder.html, 1997

[3] LAMPSON, B. W.; REDELL, D. D.: Experiences with Processes and Monitors in Mesa. In: Communications of the ACM 23 (1980), Febr., Nr. 2, S. 105–117

[4] PAPAMARCOS, M. S.; PATEL, J. H.: A Low-Overhead Coherence Solution for Multiprocessors with Private Cache Memories. In: Proceedings of the 11th Annual International Symposium on Computer Architecture (ISCA '84), June 5-7, 1984, Ann Arbor, Michigan, USA, ACM Press, 1984, S. 348-354

[5] WILNER, D. : Vx-Files: What really happened on Mars? Keynote at the 18th IEEE Real-Time Systems Symposium (RTSS '97), Dez. 1997 C | X-4 Befehlssatzebene

5 Zusammenfassung

### Resümee

- Unterbrechungssteuerung ist leicht, aber nicht immer zweckmäßig

- verlangt von den Prozessen besondere Rechte: privilegierte Befehle

- unbeteiligte gleichzeitige Prozesse werden unnötig ausgesperrt

- externe Ereignisse (Interrupts) können verloren gehen

- ungeeignet für Multi(kern)prozessorsysteme: lokale Signifikanz

- die Schlossvariable kommt meist mit Umlaufsperre zum Einsatz

- pessimistischer Ansatz zum Schutz kritischer Abschnitte: leicht

- gleichzeitige Prozesse werden als sehr wahrscheinlich angenommen

- bezogen auf den jeweils zu schützenden kritischen Abschnitt

- im Regelfall bedingen Leistungsanforderungen sensitive Verfahren

- Häufigkeit von "read-modify-write"-Zyklen pro Durchlauf minimieren

- prozessspezifisches Zurücktreten vom erneuten Schließversuch mit TAS

- variable Wartezeiten, um Konflikte bei Wiederholungen zu vermeiden

- als blockierende Synchronisation besteht hohe Verklemmungsgefahr

- **nichtblockierende Synchronisation** ist frei von Verklemmungen

- optimistischer Ansatz zum Schutz kritischer Abschnitte: schwer

- die Verfahren müssen ebenfalls sensitiv für Plattformeigenschaften sein

©wosch,jk (Lehrstuhl Informatik 4) Systemprogrammierung SP2 # WS 2012/13 30 / 34

C | X-4 Befehlssatzebene

6 Anhang

SP2 # WS 2012/13 32 / 34

# Gliederung

- Unterbrechungssteuerung

- Prinzip

- Implementierung

- - Definition

- Implementierung

- Diskussion

- Nichtblockierende Synchronisation

- Prinzip

- Elementaroperation

- Anwendung

- Diskussion

- 5 Anhang

C | X-4 Befehlssatzebene 6.1 Umlaufsperre

## Zurücktreten vom aktiven Warten mit Prozessorabgabe

```

void lv_backoff(lock_t *lock) {

time_t t0, t1, t2;

t0 = ps_pitch(pd_being());

t1 = t_stamp();

lv_suspend(lock);

t2 = t_stamp();

if (t_pitch(t1, t2) < t0)

ps_delay(t0 - t_pitch(t1, t2));

```

### Prozessverwaltung

ps\_pitch definiert den Abstand zum nächsten Versuch ps\_delay verzögert den Prozess: Prozessorabgabe

## Zeitverwaltung

t\_stamp liefert einen Zeitwert t\_pitch berechnet Zeitabstand

#### Beachte: Benutzte Abstraktionsebene

- Prozessorabgabe setzt ein Prozesskonzept voraus, das typischerweise von einem Betriebssystem bereitgestellt wird

- in dieser Implementierungsvariante wird die Umlaufsperre zu einem Konzept der Maschinenprogrammebene

C | X-4 Befehlssatzebene 6.1 Umlaufsperre

# Prozessorabgabe: passives Warten auf Freigabe der Sperre

```

Laufbereit bleibend

void lv_suspend(lock_t *lock) {

ps_forgo();

```

Effektivität hängt stark ab von der Umplanungsstrategie:

RR der Prozess kommt ans Ende der Bereitliste

sonst seine (stat./dyn.) Priorität bestimmt die Listenposition

- ggf. landet er ganz vorne

- so dass er weiterläuft ② }

```

Sperrfreigabe erwartend

```

```

void lv_suspend(lock_t *lock) {

ps_sleep(&lock->bell);

```

### schlafen legende Schlossvariable (engl. *sleeping lock*)

Bedingungssynchronisation

```

Angepasste Sperrfreigabe

```

```

void lv_release (lock_t *lock) {

lock \rightarrow bolt = 0;

ps_rouse(lock);

```

### Wach bleiben oder schlafen legen...

• eine Frage des jew. Anwendungsprofils und der Einplanungsstrategie

©wosch,jk (Lehrstuhl Informatik 4)

Systemprogrammierung

SP2 # WS 2012/13

©wosch,jk (Lehrstuhl Informatik 4)

Systemprogrammierung

SP2 # WS 2012/13 34 / 34