# Concurrent Systems

Nebenläufige Systeme

XIV. Pickings

Wolfgang Schröder-Preikschat

February 11, 2021

# Agenda

Recapitulation Concurrent Systems

Perspectives

Parallel Systems

Computing Equipment

Further Education

### Outline

# Recapitulation Concurrent Systems

Perspectives

Parallel Systems

Computing Equipment

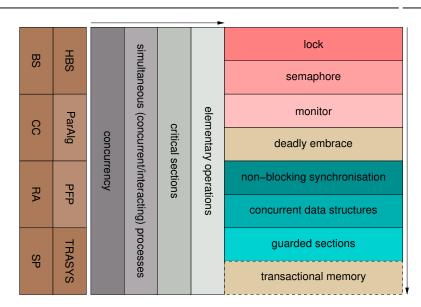

### Content of Teaching and Cross-References

### Outline

Recapitulation

Concurrent Systems

Perspectives

Parallel Systems

Computing Equipment

Further Education

- **composability** and **configurability**

- application-oriented (varying, type-safe) system software

- specialisation

- dedicated operating systems: integrated, adaptive, parallel

### reliability

gentle fault and intrusion tolerance

#### thriftiness

resource-aware operation of computing systems

#### timeliness

migration paths between time- and event-triggered real-time systems

• coordination of cooperation and competition between processes

- composability and configurability

- application-oriented (varying, type-safe) system software

- specialisation

- dedicated operating systems: integrated, adaptive, parallel

- reliability

- gentle fault and intrusion tolerance

- thriftiness

- resource-aware operation of computing systems

- timeliness

- migration paths between time- and event-triggered real-time systems

- concurrency

- coordination of cooperation and competition between processes

$<sup>^1</sup>$ http://univis.uni-erlangen.de o Research projects o LAOS

### latency prevention

- lock- and wait-free synchronisation

- integrated generator-based approach

#### latency avoidance

- interference protection

- race-conflict containment

### latency hiding

- operating-system server cores

- asynchronous remote system operation

### latency prevention

- lock- and wait-free synchronisation

- integrated generator-based approach

#### latency avoidance

- interference protection

- race-conflict containment

### latency hiding

- operating-system server cores

- asynchronous remote system operation

- process-/event-based and hardware-centric operating-system kernels

- LAKE. Sloth

### latency prevention

- lock- and wait-free synchronisation

- integrated generator-based approach

#### latency avoidance

- interference protection

- race-conflict containment

### latency hiding

- operating-system server cores

- asynchronous remote system operation

- process-/event-based and hardware-centric operating-system kernels

- LAKE. Sloth

- DFG: 2 doctoral researchers, 2 student assistants

#### event-based minimal kernel

- cache-aware main-memory footprint

- hyper-threading of latent actions

- event-based minimal kernel

- cache-aware main-memory footprint

- hyper-threading of latent actions

- featherweight agreement protocols

- overall kernel-level synchronisation

- families of consistency kernels

- event-based minimal kernel

- cache-aware main-memory footprint

- hyper-threading of latent actions

- featherweight agreement protocols

- overall kernel-level synchronisation

- families of consistency kernels

- problem-oriented consistency

- sequential, entry, release consistency

- functional hierarchy of consistency domains

- memory domains for NUMA architectures

- event-based minimal kernel

- cache-aware main-memory footprint

- hyper-threading of latent actions

- featherweight agreement protocols

- overall kernel-level synchronisation

- families of consistency kernels

- problem-oriented consistency

- sequential, entry, release consistency

- functional hierarchy of consistency domains

- memory domains for NUMA architectures

- implementation as to different processor architectures

- partial or total, resp. {in,}coherent shared memory

$<sup>^2</sup>$ http://univis.uni-erlangen.de o Research projects o COKE

- event-based minimal kernel

- cache-aware main-memory footprint

- hyper-threading of latent actions

- featherweight agreement protocols

- overall kernel-level synchronisation

- families of consistency kernels

- problem-oriented consistency

- sequential, entry, release consistency

- functional hierarchy of consistency domains

- memory domains for NUMA architectures

- implementation as to different processor architectures

- partial or total, resp. {in,}coherent shared memory

- DFG: 2 doctoral researchers (1 FAU, 1 BTU)

$<sup>{}^{2}\</sup>mathtt{http://univis.uni-erlangen.de} \rightarrow \mathsf{Research} \ \mathsf{projects} \rightarrow \mathsf{COKE}$

scalable synchronisation on the basis of agile critical sections

infrastructure • load-dependent and self-organised change of protection against race conditions

linguistic support preparation, characterisation, and capturing of declared critical sections

$<sup>^3</sup>$ http://univis.uni-erlangen.de o Research projects o PAX

scalable synchronisation on the basis of agile critical sections

infrastructure • load-dependent and self-organised change of protection against race conditions

linguistic support preparation, characterisation, and capturing of declared critical sections

- automated extraction of critical sections

- notation language for critical sections

- program analysis and LLVM integration/adaptation

$<sup>^3</sup>$ http://univis.uni-erlangen.de o Research projects o PAX

scalable synchronisation on the basis of agile critical sections

infrastructure • load-dependent and self-organised change of protection against race conditions

linguistic support preparation, characterisation, and capturing of declared critical sections

- automated extraction of critical sections

- notation language for critical sections

- program analysis and LLVM integration/adaptation

- power-aware system programming

- mutual exclusion, guarded sections, transactions

- dynamic dispatch of synchronisation protocols or critical sections, resp.

PAX

$<sup>^3</sup>$ http://univis.uni-erlangen.de o Research projects o PAX

scalable synchronisation on the basis of agile critical sections

infrastructure • load-dependent and self-organised change of protection against race conditions

linguistic support preparation, characterisation, and capturing of declared critical sections

- automated extraction of critical sections

- notation language for critical sections

- program analysis and LLVM integration/adaptation

- power-aware system programming

- mutual exclusion, guarded sections, transactions

- dynamic dispatch of synchronisation protocols or critical sections, resp.

- tamper-proof power-consumption measuring

- instruction survey and statistics based on real and virtual machines

- energy-consumption prediction or estimation, resp.

$<sup>^3</sup>$ http://univis.uni-erlangen.de o Research projects o PAX

scalable synchronisation on the basis of agile critical sections

infrastructure • load-dependent and self-organised change of protection against race conditions

linguistic support preparation, characterisation, and capturing of declared critical sections

- automated extraction of critical sections

- notation language for critical sections

- program analysis and LLVM integration/adaptation

- power-aware system programming

- mutual exclusion, guarded sections, transactions

- dynamic dispatch of synchronisation protocols or critical sections, resp.

- tamper-proof power-consumption measuring

- instruction survey and statistics based on real and virtual machines

- energy-consumption prediction or estimation, resp.

- DFG: 2 doctoral researchers, 2 student assistants

$^3$ http://univis.uni-erlangen.de o Research projects o PAX

- real-time capable network communication

- transport channel for cyber-physical systems

- predictable transmission latency

- in a certain extent guaranteed quality criteria

- real-time capable network communication

- transport channel for cyber-physical systems

- predictable transmission latency

- in a certain extent guaranteed quality criteria

#### deterministic run-time support

Auffassung von der kausalen [Vor]bestimmtheit allen Geschehens bzw. Handelns (Duden)

- latency-aware communication endpoints, optimised protocol stack

- specialised resource management, predictable run-time behaviour

$<sup>^4</sup>$ http://univis.uni-erlangen.de o Research projects o LARN

- real-time capable network communication

- transport channel for cyber-physical systems

- predictable transmission latency

- in a certain extent guaranteed quality criteria

#### deterministic run-time support

Auffassung von der kausalen [Vor]bestimmtheit allen Geschehens bzw. Handelns (Duden)

- latency-aware communication endpoints, optimised protocol stack

- specialised resource management, predictable run-time behaviour

- in time (phase 1) and energy (phase 2) respect

$<sup>^4</sup>$ http://univis.uni-erlangen.de o Research projects o LARN

- real-time capable network communication

- transport channel for cyber-physical systems

- predictable transmission latency

- in a certain extent guaranteed quality criteria

#### deterministic run-time support

Auffassung von der kausalen [Vor]bestimmtheit allen Geschehens bzw. Handelns (Duden)

- latency-aware communication endpoints, optimised protocol stack

- specialised resource management, predictable run-time behaviour

- in time (phase 1) and energy (phase 2) respect

- DFG: doctoral researchers, 2 student assistants (1 FAU, 1 Uni SB)

$<sup>^4</sup>$ http://univis.uni-erlangen.de o Research projects o LARN

# Run-Time Support System for Invasive Computing

# Run-Time Support System for Invasive Computing

#### Octo

- borrowed from the designation of a creature that:

i is highly parallel in its actions and

ii excellently can adapt oneself to its environment

- the kraken (species *Octopoda*)

- can operate in parallel by virtue of its eight tentacle

- is able to do customisation through camouflage and deimatic displays and

6

- comes with a highly developed nervous system

- in order to attune to dynamic ambient conditions and effects

#### POS

- abbrv. for parallel operating system

- an operating system that not only supports parallel processes

- but that also functions inherently parallel thereby

# Run-Time Support System for Invasive Computing

#### Octo

- borrowed from the designation of a creature that: i is highly parallel in its actions and ii excellently can adapt oneself to its environment

- the kraken (species Octopoda)

- can operate in parallel by virtue of its eight tentacle

- is able to do customisation through camouflage and deimatic displays and

6

- comes with a highly developed nervous system

- in order to attune to dynamic ambient conditions and effects

#### POS

- abbrv. for parallel operating system

- an operating system that not only supports parallel processes

- but that also functions inherently parallel thereby

- DFG: 2.5 doctoral researchers, 1 research/3 student assistants

# Multi/Many-Core Processor Pool

| faui4*  | clock              | cores per domain |         | domain |      | #    |            |

|---------|--------------------|------------------|---------|--------|------|------|------------|

|         |                    | physical         | logical | NUMA   | tile | #    |            |

| *8e     | 2.9 GHz            | 8                | 16      | 2      | 1    | 32   | Xeon       |

| *8f     | 2.9 0112           |                  | 10      | _      | _    | 32   | Xeon       |

| *9big01 | 2.5 GHz            | 6                | 6       | 8      | 1    | 48   | Opteron    |

| *9big02 | 2.2 GHz            | 10               | 20      | 4      | 1    | 80   | Xeon       |

| *9big03 | 2.1 GHz            | 12               | 24      | 4      | 1    | 96   | Xeon       |

| *9big04 | 2 GHz <sup>6</sup> | 64               | 128     | 2      | 1    | 256  | Ерус       |

| *9big05 | 2.5 GHz            | 16               | 128     | 2      | 4    | 1024 | ThunderX2  |

| *9phi01 | 1.2 GHz            | 6                | 12      | 2      | 1    | 24   | Xeon       |

|         | 1.1 GHz            | 57               | 228     | 2      | 1    | 456  | Xeon Phi   |

| *scc    | 1.5 GHz            | 4                | 8       | 1      | 1    | 8    | Xeon       |

|         | 800 MHz            | 2                | _       | _      | 24   | 48   | Pentium    |

| fastbox | 3.5 GHz            | 4                | 8       | 1      | 1    | 8    | Xeon TSX   |

| InvasIC | 50 MHz             | 5                | 5       | 16     |      | 80   | LEON/SPARC |

2160

<sup>6</sup>mit boost 3.35 GHz

# Bachelor, Master, or Doctoral Thesis