# Memory Protection at Option

Application-Tailored Memory Safety in Safety-Critical Embedded Systems

Speicherschutz nach Wahl

Auf die Anwendung zugeschnittene Speichersicherheit in sicherheitskritischen eingebetteten Systemen

Der Technischen Fakultät der Universität Erlangen-Nürnberg

zur Erlangung des Grades

# Doktor-Ingenieur

vorgelegt von

Michael Stilkerich

${\rm Erlangen}-2012$

Als Dissertation genehmigt von der Technischen Fakultät Universität Erlangen-Nürnberg

| Tag der Einreichung: | 09.07.2012                                |

|----------------------|-------------------------------------------|

| Tag der Promotion:   | 30.11.2012                                |

| Dekan:               | Prof. DrIng. Marion Merklein              |

| Berichterstatter:    | Prof. DrIng. Wolfgang Schröder-Preikschat |

|                      | Prof. Dr. Michael Philippsen              |

# Abstract

With the increasing capabilities and resources available on microcontrollers, there is a trend in the embedded industry to integrate multiple software functions on a single system to save cost, size, weight, and power. The integration raises new requirements, thereunder the need for spatial isolation, which is commonly established by using a memory protection unit (MPU) that can constrain access to the physical address space to a fixed set of address regions. MPU-based protection is limited in terms of available hardware, flexibility, granularity and ease of use. Software-based memory protection can provide an alternative or complement MPU-based protection, but has found little attention in the embedded domain.

In this thesis, I evaluate qualitative and quantitative advantages and limitations of MPU-based memory protection and software-based protection based on a multi-JVM. I developed a framework composed of the AUTOSAR OS-like operating system CiAO and KESO, a Java implementation for deeply embedded systems. The framework allows choosing from no memory protection, MPU-based protection, software-based protection, and a combination of the two. This decision can be made individually for each protection realm in the system. For both MPU- and software-based protection, the framework provides different trade-offs between the cost and the provided level of protection.

To achieve the configurability of MPU-based protection, I use aspect-oriented techniques to integrate the necessary changes to the operating system and the application. The configurability of software-based protection is based on static analyses in the Java compiler. The results of these analyses are also leveraged to improve the effectivity of MPU-based protection by aiding to determine private code and data items at a fine-grained level, showing significant improvements over the mostly manual existing approach in CiAO. The framework is completed by an extension that offers a soft-migration approach for existing applications.

At the example of the control software for a quadrotor helicopter, I evaluate the cost of using Java instead of the spread C or C++ languages and the qualitative and quantitative pros and cons of the different memory protection mechanisms. The evaluation shows that a Java implementation tailored towards the application domain can provide competitive performance to C and C++, but provides the added value of comprehensive software-based memory safety. The comparison of MPU-based and software-based protection showed that either can be more efficient depending on the type of application. The existence of both approaches is justified, and the two approaches complement each other in many aspects, which makes a combination of the two feasible as well.

## Zusammenfassung

Zur räumlichen Isolation verschiedener Anwendungen auf einem Mikrokontroller wird im Umfeld zutiefst eingebetteter, statisch-konfigurierter Systeme üblicherweise eine Speicherschutzeinheit (MPU) eingesetzt. Diese beschränkt Speicherzugriffe auf eine begrenzte Zahl von Adressbereichen. MPU-basierter Speicherschutz zeigt jedoch Einschränkungen in den Bereichen der Hardwareauswahl, der Flexibilität und Granularität des gebotenen Speicherschutzes sowie des Aufwands der Benutzung. Softwarebasierte Verfahren bieten eine Alternative oder Ergänzung, haben bislang im Bereich der eingebetteten Systeme jedoch kaum Beachtung gefunden.

Diese Dissertation betrachtet vergleichend die qualitativen und quantitativen Vorteile und Einschränkungen von MPU-basiertem Speicherschutz und Speicherschutz basierend auf einer Multi-JVM. Aufbauend auf CiAO, einem Betriebssystem mit einer AUTOSAR OS Schnittstelle, und KESO, einer Java Laufzeitumgebung für zutiefst eingebettete Systeme, wurde ein Rahmenwerk entwickelt, welches die freie Wahl zwischen beiden Verfahren sowie deren Kombination erlaubt. Diese Entscheidung kann individuell für jeden Schutzraum im System getroffen werden. Das Rahmenwerk unterstützt für beide Verfahren verschiedene Abstimmungsgrade zur Beeinflussung des Verhältnisses von Kosten und gebotenem Schutzgrad.

Zur Realisierung des konfigurierbaren MPU-basierten Speicherschutzes wurden aspektorientierte Techniken verwendet, um die notwendigen Anpassungen in das Betriebssystem sowie die Anwendung einzubringen. Die Konfigurierbarkeit des softwarebasierten Schutzes basiert auf statischen Programmanalysen im Java-Übersetzer, deren Ergebnisse auch zur Identifikation privater Programmteile und Datenstrukturen verwendet wurden. Hierdurch konnte die Effektivität des MPU-basierten Speicherschutzes im Vergleich zum vorhandenen, größtenteils manuellen Ansatz in CiAO deutlich gesteigert werden. Eine Erweiterung zur Unterstützung eines weichen Migrationsansatzes für bestehende Anwendungen vervollständigt das Rahmenwerk.

Am Beispiel der Steueranwendung eines Quadrokopters wurden die Kosten für die Nutzung von Java als Ersatz für die verbreiteten Sprachen C und C++ evaluiert, sowie die qualitativen und quantitativen Vor- und Nachteile der verschiedenen Speicherschutzverfahren untersucht. Die Ergebnisse zeigen, dass die Verwendung einer auf die Anwendungsdomäne zugeschnittenen Java-Laufzeitumgebung keine Mehrkosten im Vergleich zu C und C++ mitbringen muss, jedoch den Mehrwert der umfassenden softwarebasierten Speichersicherheit bietet. Der Vergleich beider Speicherschutzverfahren ergab, dass jedes abhängig von den Anwendungseigenschaften das effizientere sein kann. Beide Verfahren haben ihre Existenzberechtigung und ergänzen sich in vielen Bereichen, so dass auch die Kombination sinnvoll sein kann.

### Acknowledgments

My years at the FAU's system software group as a research assistant were some of the most fun yet. The product of those years – this thesis – would not have been possible in this form without the support and help of my great colleagues, to whom I want to express my gratitude.

My professor Wolfgang Schröder-Preikschat enables and supports his doctoral students in pursuing their own research interests. It is the freedom and self-responsibility he grants to his students that make his group such a great environment to work in. Together with Jürgen Kleinöder, I organized the exercises accompanying the systems programming lectures for some years; he enabled me to incorporate my own ideas into the course contents and I enjoyed those years of teaching a lot.

Some of my colleagues and former students contributed to parts of this thesis: Back when I was an undergraduate student, *Christian Wawersich* raised my interest in embedded systems and safety and brought me into the KESO project. *Daniel Lohmann* helped me throughout my research with invaluable discussions that often provided me with new perspectives on my research topics. *Peter Ulbrich* is the head of the I4Copter project; he not only provided me with the ideal evaluation scenario but also spent many hours helping me adapting and porting it; unforgotten, he showed very forgiving when I accidentally crashed the I4Copter into a building. *Jens Schedel* ported the I4Copter software to use the AUTOSAR OS interface and thereby made it usable for my setup. *Michael Strotz* implemented my ideas on gradual software-based memory protection in the KESO project. *Christoph Erhardt* did outstanding work on the compiler core; his work provided an important piece of infrastructure for my thesis.

My wife *Isabella* supported and motivated me in the challenging phases of thesis writing, proof-read and discussed with me the contents of this thesis.

Finally, I'd like to thank all my other colleagues that made working in the group such a great time.

Erlangen, December 2012

# Contents

| 1 | Intro | oduction                                                                                                   | 1  |

|---|-------|------------------------------------------------------------------------------------------------------------|----|

|   | 1.1   | Motivation                                                                                                 | 1  |

|   |       | 1.1.1 Electronic Control Units in the Automotive Industry                                                  | 2  |

|   |       | 1.1.2 Paradigm Shift Towards an Integrated Architecture                                                    | 3  |

|   |       | 1.1.3 New System-Software Requirements: Need for Isolation $\ldots$                                        | 3  |

|   | 1.2   | Problem Statement and Proposed Solution                                                                    | 4  |

|   | 1.3   | Broader Scope of this Work                                                                                 | 5  |

|   | 1.4   | Structure of this Thesis                                                                                   | 6  |

|   | 1.5   | Own Publications Related to this Thesis                                                                    | 7  |

| 2 | Stat  | te of the Art                                                                                              | 9  |

|   | 2.1   | Levels of Memory Protection                                                                                | 9  |

|   |       | 2.1.1 Sandboxing $\ldots$ | 9  |

|   |       | 2.1.2 Memory Safety                                                                                        | 10 |

|   |       | 2.1.3 Type Safety                                                                                          | 10 |

|   | 2.2   | Comparison Criteria                                                                                        | 11 |

|   | 2.3   | Hardware-Based Memory Protection Approaches                                                                | 13 |

|   |       | 2.3.1 Coarse-Grained Approaches Without In-Memory Data Structures                                          | 13 |

|   |       | 2.3.2 Caching Approaches with In-Memory Data Structures                                                    | 14 |

|   |       | 2.3.3 Discussion $\ldots$ | 17 |

|   | 2.4   | Software-Based Memory Protection Approaches                                                                | 18 |

|   |       | 2.4.1 Instruction-Set-Architecture-Level Approaches                                                        | 19 |

|   |       | 2.4.2 Compiler-Level Approaches                                                                            | 21 |

|   |       | 2.4.3 Language-Level Approaches                                                                            | 24 |

|   |       | 2.4.4 Discussion $\ldots$                                                                                  | 29 |

|   | 2.5   | Decision for MPU-Based Protection and a Multi-JVM                                                          | 33 |

| 3 |       | , II                                                                                                       | 35 |

|   | 3.1   | The AUTOSAR OS Application Model                                                                           | 35 |

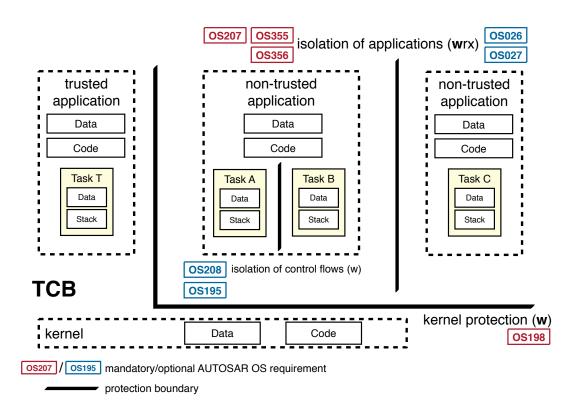

|   |       | 3.1.1 Layers of Protection                                                                                 | 36 |

|   |       | 3.1.2 Required Isolation Properties                                                                        | 37 |

|   |       | 3.1.3 Graduations of Hardware-Based Memory Protection                                                      | 38 |

|   | 3.2   | The I4Copter Application                                                                                   | 39 |

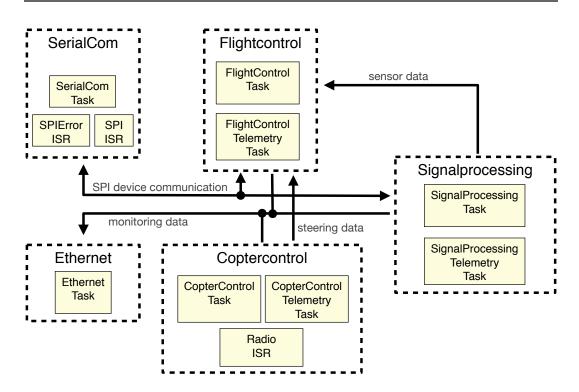

|   |       | 3.2.1 Core Subsystems of the I4Copter Framework                                                            | 39 |

|   |       | 3.2.2 Mapping to the AUTOSAR OS Application Model                                                          | 42 |

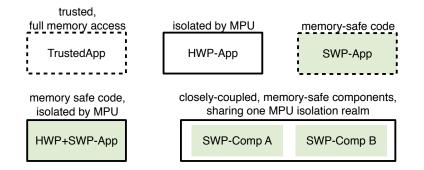

|   | 3.3 | Model  | l Refinement: Software-Isolated Components               | . 43 |

|---|-----|--------|----------------------------------------------------------|------|

|   | 3.4 | Gradu  | ations of Software-Based Memory Protection               | . 44 |

|   |     | 3.4.1  | Memory-Protection Overhead Imposed by Java               | . 44 |

|   |     | 3.4.2  | Offloading Runtime Checks to the Hardware                | . 47 |

|   |     | 3.4.3  | Selective Omission of Runtime Checks                     | . 50 |

|   |     | 3.4.4  | Impact Classification                                    | . 51 |

|   | 3.5 | Chapt  | er Summary                                               | . 56 |

| 4 | Des | ign: A | Framework that Provides Memory Protection at Option      | 59   |

|   | 4.1 | Select | ion of an AUTOSAR OS Implementation                      | . 60 |

|   |     | 4.1.1  | CiAO Application Model                                   | . 60 |

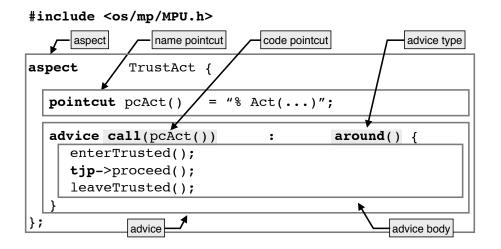

|   |     | 4.1.2  | Introduction to AspectC++                                | . 61 |

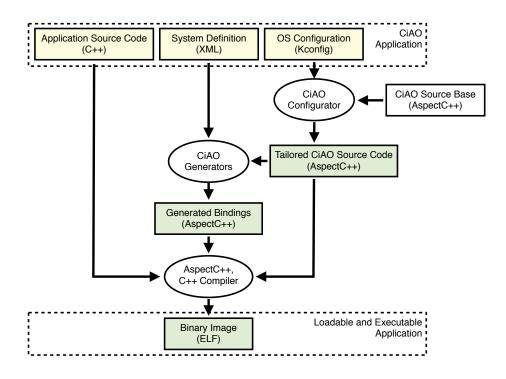

|   |     | 4.1.3  | CiAO Build Process                                       |      |

|   |     | 4.1.4  | CiAO Components: Application Interface                   | . 65 |

|   | 4.2 | Select | ion of a Multi-JVM                                       | . 66 |

|   |     | 4.2.1  | J2ME Implementations                                     | . 66 |

|   |     | 4.2.2  | Commercial JVMs for Embedded and Real-Time Systems       | . 67 |

|   |     | 4.2.3  | Sun's SquawkVM for Sensor Nodes                          | . 67 |

|   |     | 4.2.4  | KESO                                                     | . 67 |

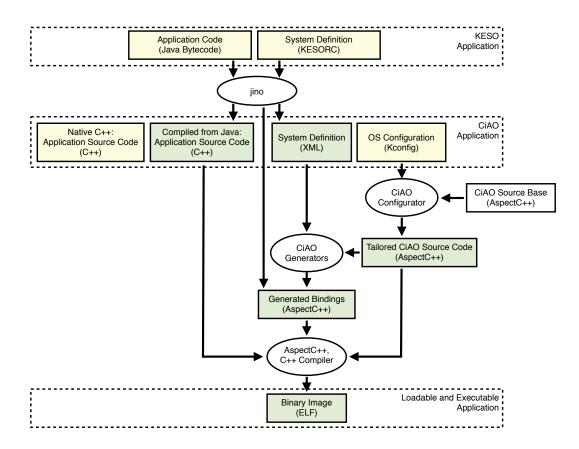

|   | 4.3 | Integr | ation of KESO with CiAO                                  | . 71 |

|   |     | 4.3.1  | CiAO Backend                                             | . 71 |

|   |     | 4.3.2  | C++-Compatible Output                                    | . 72 |

|   |     | 4.3.3  | MPU-based-Protection-Friendly Java Runtime Environment . | . 73 |

|   | 4.4 | Config | gurable MPU-Based Protection                             | . 74 |

|   |     | 4.4.1  | Region Management                                        | . 74 |

|   |     | 4.4.2  | Region Identification and Data Mapping                   | . 76 |

|   |     | 4.4.3  | Configurable MPU-Context Switching Code                  | . 78 |

|   | 4.5 | Deteri | mining Domain Reachability for Java Code                 | . 85 |

|   |     | 4.5.1  | Overview of the Reachability Analyses in Jino            | . 87 |

|   |     | 4.5.2  | Domain Reachability Example                              | . 87 |

|   |     | 4.5.3  | Reachability Results for the I4Copter Codebase           | . 89 |

|   | 4.6 | Config | gurable Software-Based Protection                        | . 89 |

|   |     | 4.6.1  | Incorporating Memory Characteristics into the Compiler   | . 91 |

|   |     | 4.6.2  | Per-Application Configurability                          | . 92 |

|   | 4.7 | Chapt  | er Summary                                               | . 93 |

| 5 | Con | nponen | t-Wise Soft Migration                                    | 95   |

|   | 5.1 | Migra  | tion Granularity: Software Components                    | . 95 |

|   |     | 5.1.1  | Considering CiAO and KESO as Component Systems           | . 96 |

|   |     | 5.1.2  | I4Copter Component Interfaces                            |      |

|   | 5.2 | Shared | d Memory Extension for CiAO                              |      |

|   |     | 5.2.1  | Definition of Shared Memory Areas                        | . 98 |

|   |     | 5.2.2  | Shared Memory Placement                                  |      |

|   |     | 5.2.3  | Shared Memory Conclusions                                |      |

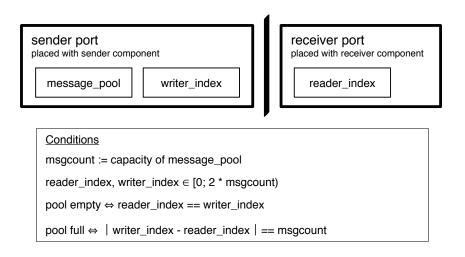

|   | 5.3        | Messa            | ge Ports for CiAO                                        | . 105 |

|---|------------|------------------|----------------------------------------------------------|-------|

|   |            | 5.3.1            | Message Protocol                                         | . 106 |

|   |            | 5.3.2            | Placement and Implementation                             | . 107 |

|   |            | 5.3.3            | Implications of Read Protection                          | . 108 |

|   |            | 5.3.4            | Variants                                                 | . 108 |

|   |            | 5.3.5            | Message Ports Conclusions                                | . 109 |

|   | 5.4        | Safe Ja          | ava Interface                                            | . 109 |

|   |            | 5.4.1            | KESO Abstractions for Accessing Raw Memory Areas         | . 109 |

|   |            | 5.4.2            | Using Memory-Mapped Objects to Resemble C Data Types .   | . 110 |

|   |            | 5.4.3            | Possible Issues with Mapping C Types to Mapped Objects   | . 111 |

|   |            | 5.4.4            | Raw Memory as a Base Abstraction                         | . 112 |

|   | 5.5        | Port o           | f the I4Copter Application                               | . 112 |

|   | 5.6        | Chapt            | er Summary                                               | . 112 |

| _ | •          |                  |                                                          |       |

| 6 | -          |                  | e Evaluation                                             | 115   |

|   | 6.1        |                  | etup                                                     |       |

|   |            | 6.1.1            | Evaluation Platform                                      |       |

|   | C O        | 6.1.2            | Used Compilers and Tools                                 |       |

|   | 6.2        |                  | Applications                                             |       |

|   |            | $6.2.1 \\ 6.2.2$ | I4Copter                                                 |       |

|   | 69         | -                | Collision Detector Benchmark Family                      |       |

|   | 6.3        |                  | es and Method of Measurement                             |       |

|   |            | 6.3.1            | Statically Determined Metrics                            |       |

|   | <i>C</i> 1 | 6.3.2<br>Carta   | Runtime Measurements                                     |       |

|   | 6.4        |                  | f Using Java Instead of C or C++ $\dots$                 |       |

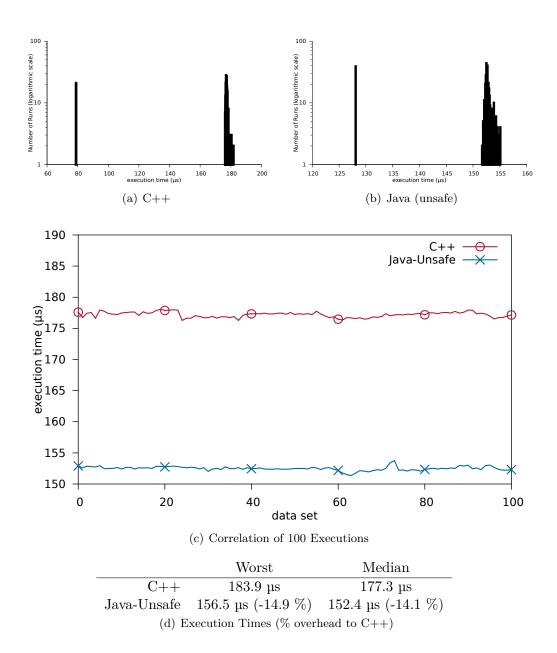

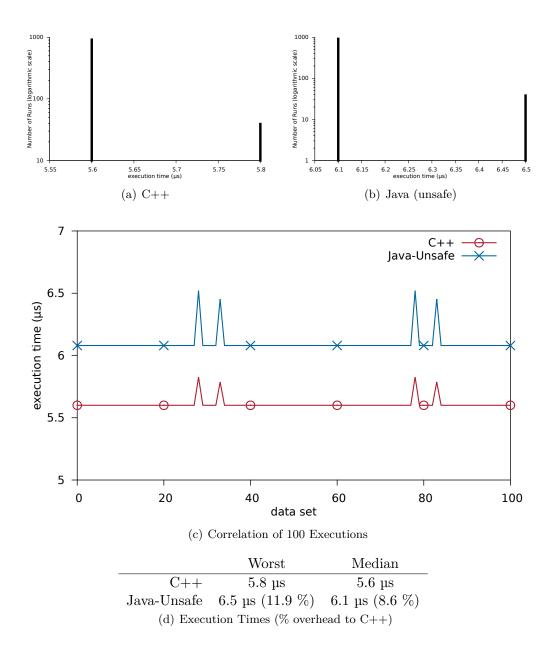

|   |            | $6.4.1 \\ 6.4.2$ | I4Copter                                                 |       |

|   |            | 0.4.2<br>6.4.3   | Collision Detector                                       |       |

|   | 6.5        | 0 0              | penchmarks: Individual Costs of Basic Operations         |       |

|   | 0.0        | 6.5.1            | Basic Protection Primitives                              |       |

|   |            | 6.5.2            | Costs of Common System Operations                        |       |

|   |            | 6.5.2            | Conclusions                                              |       |

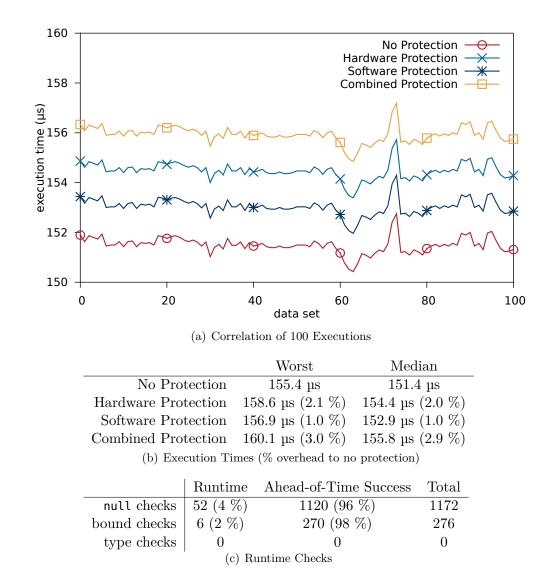

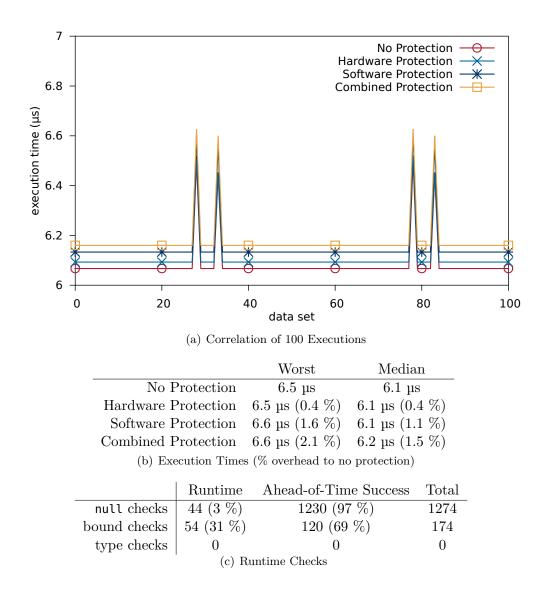

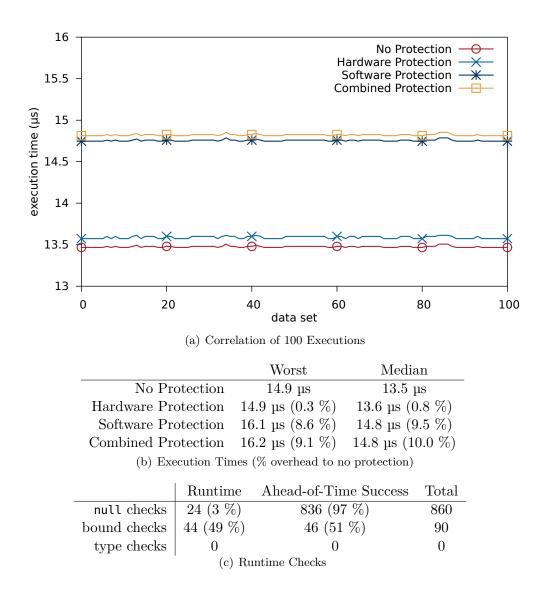

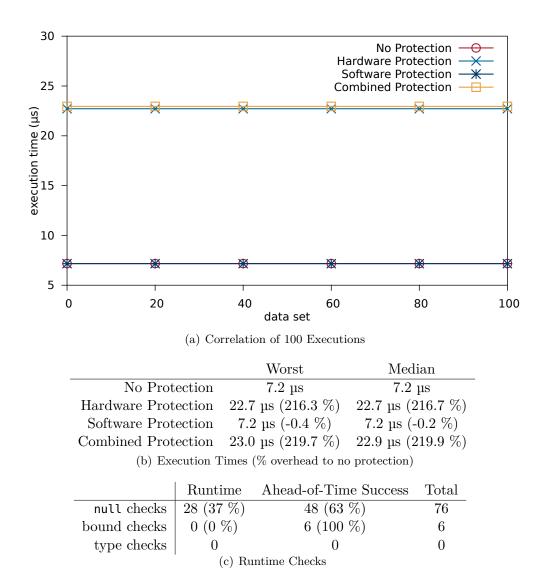

|   | 6.6        | 0.0.0            | of Memory Protection in the I4Copter                     |       |

|   | 0.0        | 6.6.1            | Execution Times                                          |       |

|   |            | 6.6.2            | Memory Footprint                                         |       |

|   |            | 6.6.3            | Conclusions                                              |       |

|   | 6.7        |                  | er Summary                                               |       |

|   | 0          | 6.7.1            | Overhead of Using Java as a Language Compared to $C/C++$ |       |

|   |            | 6.7.2            | Costs of Basic Protection Primitives                     |       |

|   |            | 6.7.3            | Comparison of Protection Mechanisms for an Application   |       |

| 7 | Sun        | nmary. (         | Conclusions, and Outlook                                 | 153   |

|   | 7.1        | -                | ary                                                      |       |

|   | 7.2        |                  | isions                                                   |       |

|   |            |                  |                                                          |       |

| 7.3 | Contributions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $15$                          | 5 |

|-----|------------------------------------------------------------------------------------------------------------------------------|---|

| 7.4 | Ideas for Future Work $\ldots \ldots 15$ | 6 |

# List of Figures

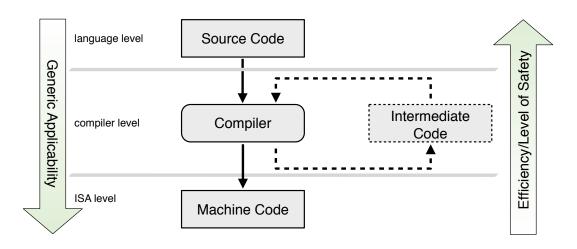

| 2.1  | Levels of Application of Software-Based Memory Protection 18                                           |

|------|--------------------------------------------------------------------------------------------------------|

| 3.1  | The AUTOSAR OS Application Model                                                                       |

| 3.2  | Photo of the I4Copter, Version 2.4 ("Apollo")                                                          |

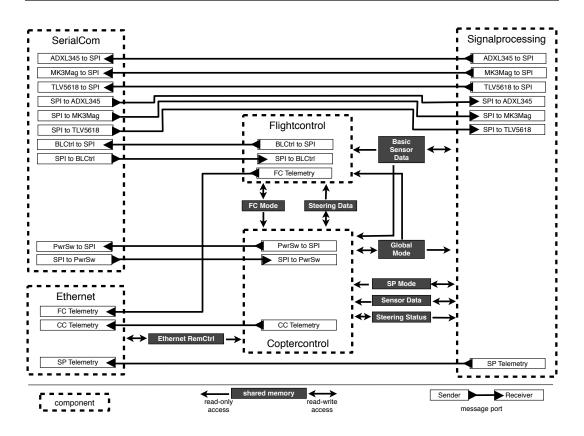

| 3.3  | Subsystems and Data Exchange Paths in the I4Copter 40                                                  |

| 3.4  | Isolation Variants                                                                                     |

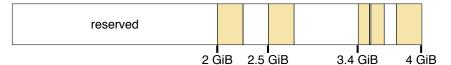

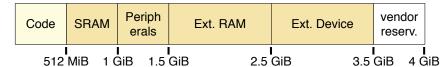

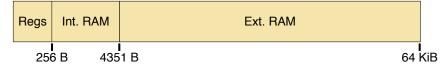

| 3.5  | Example Address Space Utilizations                                                                     |

| 4.1  | AspectC++ Syntax Example                                                                               |

| 4.2  | CiAO Build Process                                                                                     |

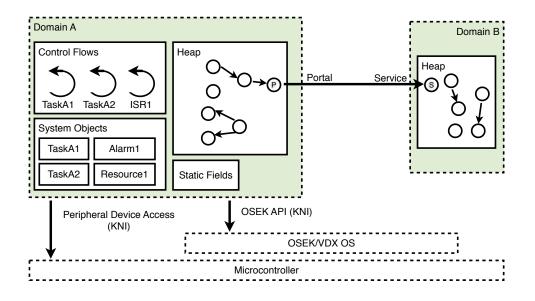

| 4.3  | KESO: Architecture, Domains and Inter-Domain Communication $$ 69                                       |

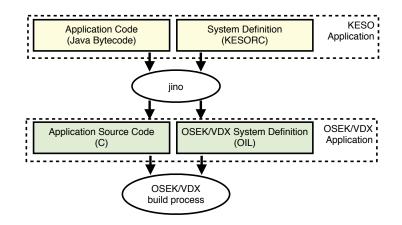

| 4.4  | KESO Build Process                                                                                     |

| 4.5  | KESO and CiAO Combined                                                                                 |

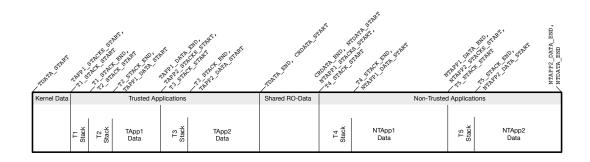

| 4.6  | Configuration-Independent Memory Layout (Data Only) 78                                                 |

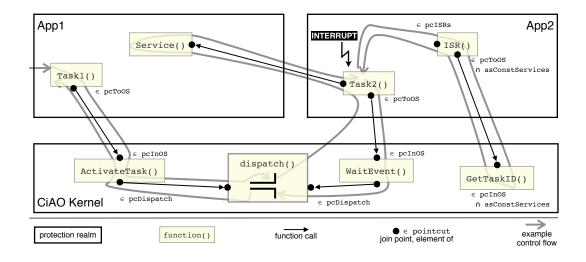

| 4.7  | Protection Context Switching                                                                           |

| 4.8  | Domain-Specific Rapid Type Analysis and Reachability Analysis 88                                       |

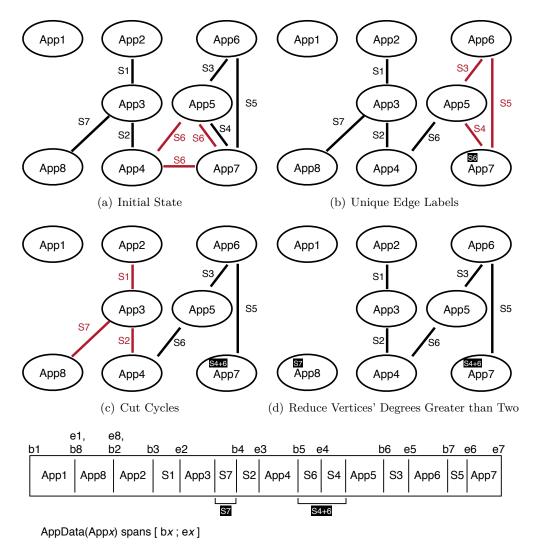

| 5.1  | I4Copter Component Interfaces                                                                          |

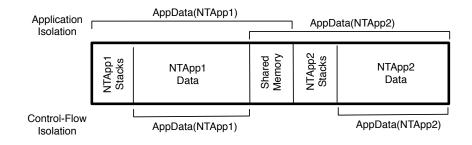

| 5.2  | Shared Memory Placement by Overlapping Private Data Segments $\ . \ . \ 101$                           |

| 5.3  | Example: Shared Memory Dependencies Among OS-Applications 103                                          |

| 5.4  | Basic Message Port Implementation and Placement                                                        |

| 5.5  | Mapping C Data Types to KESO's Memory-Mapped Objects 110                                               |

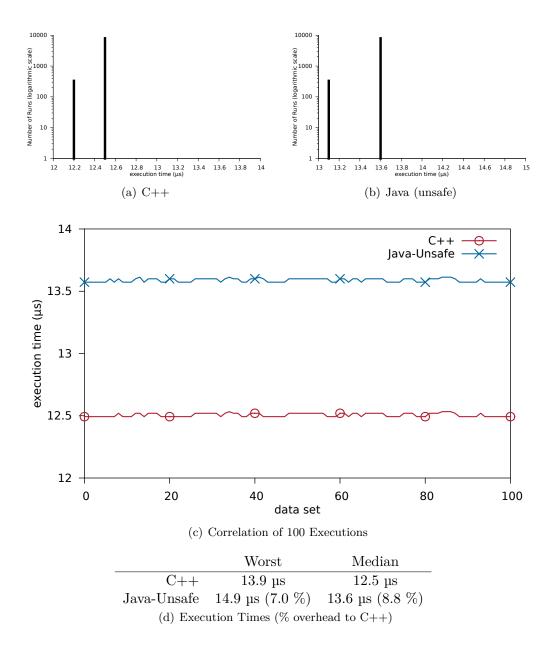

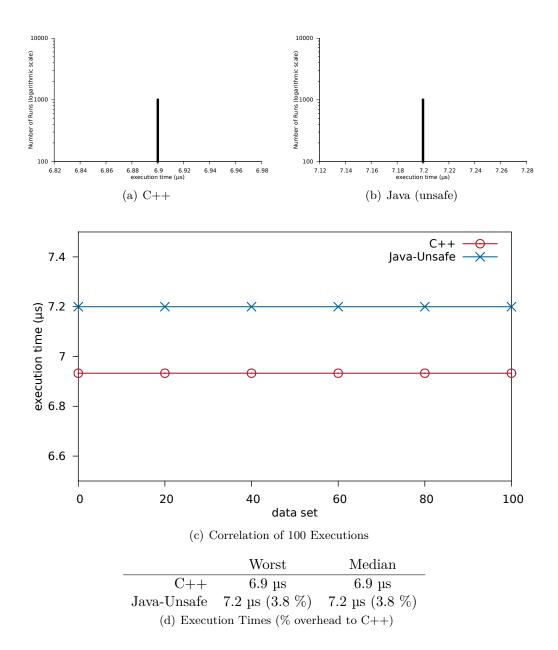

| 6.1  | Flightcontrol: Execution Time Comparison C++ Versus Java 123                                           |

| 6.2  | Copter<br>control: Execution Time Comparison C++ Versus Java $\ . \ . \ . \ 125$                       |

| 6.3  | Signal<br>processing: Execution Time Comparison C++ Versus Java $\ . \ . \ . \ 126$                    |

| 6.4  | SerialCom: Execution Time Comparison C++ Versus Java $\ \ldots \ \ldots \ 128$                         |

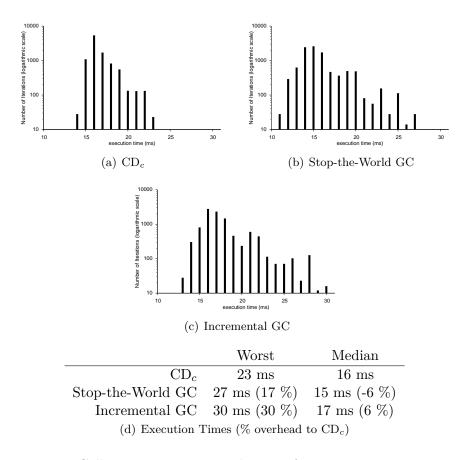

| 6.5  | Collision Detector: Distribution of Iteration Execution Times $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ |

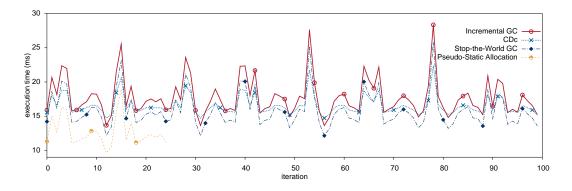

| 6.6  | Collision Detector: Execution Times for 100 Iterations                                                 |

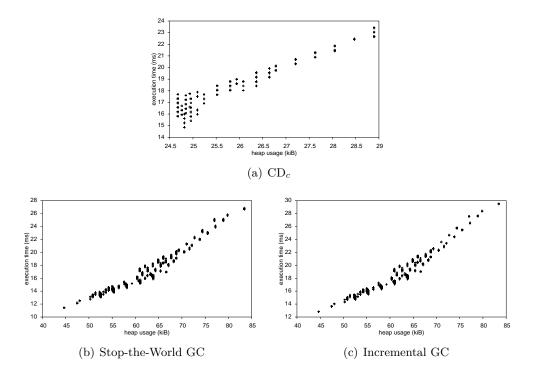

| 6.7  | Correlation Between Heap Usage and Execution Time $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $             |

| 6.8  | Flight<br>control: Comparison of Protection Variants                                                   |

| 6.9  | Copter<br>control: Comparison of Protection Variants $\ \ldots \ \ldots \ \ldots \ \ldots \ 143$       |

| 6.10 | Signal<br>processing Comparison of Protection Variants $\hfill \ldots \ldots \ldots 145$               |

| 6.11 | SerialCom Comparison of Protection Variants                                                            |

# List of Tables

| 2.1 | Comparison of Memory Protection Mechanisms                           | 32  |

|-----|----------------------------------------------------------------------|-----|

| 3.1 | Memory Protection Requirements from the AUTOSAR OS Specification     | 37  |

| 3.2 | Control Flows' Properties in the I4Copter                            | 42  |

| 3.3 | Checked JVM Instructions                                             | 45  |

| 3.4 | Frequency of Checked Instructions                                    | 51  |

| 3.5 | Impact Classification                                                | 52  |

| 4.1 | Data Region Definitions for Read-Write Protection                    | 78  |

| 4.2 | Domain Reachability of Types and Code in the I4Copter                | 90  |

| 5.1 | Shared Memory Uses in the I4Copter                                   | 100 |

| 5.2 | Shared Memory Placement in the I4Copter                              | 100 |

| 6.1 | I4Copter Memory Footprint: C++ Versus Java                           | 29  |

| 6.2 | Specialization Versus Generalization: I4Copter Gyroscope Driver 1    | 131 |

| 6.3 | $CD_x$ Footprint                                                     | 136 |

| 6.4 | Costs of Basic Protection Primitives                                 | 138 |

| 6.5 | System Operations' Runtime with Different Levels of MPU Protection 1 | 139 |

| 6.6 | I4Copter Memory Footprint: Different Memory Protection Variants . 1  | 48  |

# Listings

| $2.1 \\ 2.2$ | Deputy Annotations for memcpy()                                      |     |

|--------------|----------------------------------------------------------------------|-----|

| 3.1          | Example: Array Access                                                | 55  |

| 4.1          | CiAO Component Definition                                            | 65  |

| 4.2          | Pointcuts of the Memory Protection Subsystem for Write Protection .  | 81  |

| 4.3          | Aspect that Provides Privileged Mode Switching for System Services . | 83  |

| 4.4          | TC1796 Memory Characteristics Description                            | 91  |

| 5.1          | Shared Memory Definition                                             | 99  |

| 5.2          | Message Port Definition                                              | 106 |

| 6.1          | Shared Memory Access (Java Code)                                     | 132 |

| 6.2          | Shared Memory Access (Generated C Code)                              | 132 |

# Introduction

#### 1.1 Motivation

With eight billion units deployed in the year 2000, embedded microprocessors pose the lion's share of processors as opposed to 150 million general-purpose computers sold in the same year [117]. An embedded system is a computer system developed and deployed for a special purpose. Embedded systems are becoming increasingly ubiquitous in our everyday lives and are found, for example, in household appliances or cars.

Embedded systems are often part of a mass product and subject to an immense cost pressure. Cost differences of few cents for a single unit accumulate to a considerable amount for the whole of produced units. The microcontroller manufacturers commonly offer a product line of derivates around a specific microcontroller core. The derivates differ in features such as the amount of on-chip program and data memory, the number of I/O pins or the availability of optional functional units such as a memory protection unit (MPU) or communication interfaces such as CAN, SPI or UART. As a concrete example, STMicroelectronics' STM32F1 line of mainstream ARM Cortex-M3 processors as of 2011 offers derivates with program flash from 16 KiB to 1 MiB and RAM from 4 KiB to 96 KiB. The price range in this line for large quantities ranges from  $1.76 \in (STM32F100C4T6B, 16 KiB ROM, 4 KiB RAM)$  to  $15.23 \in (STM32F103ZGT6, 1MiB ROM, 96 KiB RAM)$  at a large retailer<sup>1</sup> – the largest derivate is more than eight times the price of the smallest one.

$<sup>^{1}\</sup>mathrm{Prices}$  from http://de.farnell.com with the highest listed high-quantity rebate, retrieved on December 13, 2011

#### 1.1.1 Electronic Control Units in the Automotive Industry

One industry where the electronic functionality has rapidly grown over the past decade is the automotive industry. A 2006 article [20] talks about ten million lines of code in a premium car, whereas a more recent Bosch article [78] already gives the number of up to 100 million lines of code in a luxury car. These numbers show the enormous growth of software in the automotive sector.

Embedded systems in a modern car take control of a wide-range of functionalities, covering comfort functions such as the fully automatic control of the air conditioning to safety-critical functions such as the anti-lock braking system (ABS) or the electronic stability program (ESP). With the trend towards more fuel-efficient cars that require sophisticated engine control and the introduction of electric cars, it is probable that the significance of electronic functions and the amount of software will continue to grow.

The automotive industry is vertically organized, that is, most of the development is carried out by a multitude of component suppliers. Traditionally, the electronic control units (ECUs) that implement electronic functions of a car have been shipped as black boxes comprising both the hardware and the software to the car manufacturer (OEM) [48]. The OEM then needed to integrate these black boxes by connecting them through communication busses such as the controller-area network (CAN) to form a cooperating network. In this *federated architecture* a dedicated microcontroller exists for each electronic function. A modern mid-class car is equipped with about 80 ECUs [78]. With the current amount of ECUs and the trend towards increasing electronic functionality, the federated architecture is running into a scalability problem as the integration is becoming increasingly difficult for the OEM for multiple reasons.

- **Heterogeneity:** The ECUs are provided by a multitude of component suppliers and are heterogeneous in both hardware and software. Building a network of these black boxes becomes increasingly difficult with higher numbers of ECUs.

- **Reliability:** The connectors that network the different ECUs are known to be faultprone and a major cause of hardware failures.

- Weight: The car wire harness by itself exceeds 100 kilograms in weight, comprising a length of more than two kilometers of wires. The electronic control units add additional weight. The increasing weight for cars of comparable class in recent years conflicts with the goal of fuel-efficiency.

- **Space:** The space behind the car interior linings and in the engine compartment is limited.

- **Cost:** Electronic components and software account for up to 40 percent of a car's production costs [20]. The price for copper has risen by more than 400 percent in the past decade.

#### 1.1.2 Paradigm Shift Towards an Integrated Architecture

The automotive industry is undertaking various steps to address the above issues. One is the attempt to substitute copper as the wire material for the cheaper and more lightweight, but also less conductive, aluminum. The electrical differences between the two materials raise new issues that need to be addressed. Also, while the material transition lowers the weight and cost of the wire harness, the issues of requirement for limited space and the high number of fault-prone connectors remain.

A more fundamental approach is the departure from the federated architecture and a shift towards an *integrated architecture*, where multiple software functions are co-located on a single, but more powerful ECU. This architecture scales better, as more capable microcontrollers are developed in parallel to the increase of electronic functionality that provide more resources at the same price and physical size. The integrated architecture addresses many of the above issues: Two previously networked components that are integrated on a single ECU can communicate without the need for additional wires. The reduced amount of ECUs, wires and connectors reduce the material cost and weight and space requirements and at the same time increase the mechanic reliability of the electronic system.

#### 1.1.3 New System-Software Requirements: Need for Isolation

With the shift to an integrated architecture, however, an important property of the federated architecture gets lost. With a dedicated ECU for every software function, each application executes in a physically isolated environment. A fault in one component is thereby contained and cannot directly affect the other components in the system. In addition, the faulty function can be identified relatively easy as the black box does not behave correctly and the supplier can be notified. This identification is important for both a quick resolution of the issue as well as for possible liability claims that may have been raised by the malfunctioning component.

By co-locating multiple applications on a single microcontroller on top of an OS-EK/VDX operating system [86] – the currently most-widely used operating system in the automotive domain – these properties of fault containment and easy identification of a malfunctioning component are lost, since OSEK/VDX does not provide any means for the isolated execution of multiple applications. The shift towards an integrated architecture therefore introduces new requirements for the system software, most notably in the areas of temporal and spatial isolation. The automotive industry reacted to the new requirements with the development of a new operating system standard AUTOSAR OS [10]. The designated successor to OSEK/VDX provides temporal isolation by enforcing execution time budgets, terminating tasks that exceed their supposed worst-case execution time (WCET) in one job. This prevents that the fault propagates to other applications by not leaving enough CPU time for the other applications' tasks to meet their deadlines. AUTOSAR OS also provides optional support for hardware-based memory protection on microcontrollers that are equipped with the needed memory protection unit. Memory protection provides the spatial isolation of the different applications, which ensures that a fault in one application cannot corrupt the state of another application. In my thesis, I put the focus on the issue of memory protection, but get back to the topic of temporal isolation where close correlations exist.

#### 1.2 Problem Statement and Proposed Solution

The hardware-based memory protection mechanism based on the use of an MPU is not optimal for all applications. The first obvious reason is that the chosen microcontroller needs to be equipped with an MPU, which is not the case for many low-cost chips. From the STM32F1 line discussed above, only eleven of 94 derivates in the upper-quarter price segment come with an MPU, of which the cheapest costs  $11.76 \in (STM32F103VFT6, 768 \text{ KiB ROM}, 96 \text{ KiB RAM})$ . The need for an MPU therefore constrains the available choice to few higher-end derivates, which is problematic in cost-sensitive application domains. Besides this economic downside, there are further problematic aspects associated with spatial isolation established by an MPU with respect to flexibility, the granularity of protection provided and the required developer expertise.

An alternative to using a hardware unit to achieve spatial isolation is purely softwarebased memory protection. There are various software-based techniques to establish spatially isolated applications that address many of the drawbacks of using an MPU, but none of these have so far considerably been adopted by the embedded industry. Although software-based approaches provide benefits over MPU-based protection in many aspects, they also have disadvantages in other aspects, for example execution time overhead or less robustness with respect to transient hardware errors. A more detailed discussion of the properties of different hardware- and software-based memory protection techniques follows in Chapter 2.

With both hardware- and software-based mechanisms offering advantages over the other in some aspects, it is not possible to generally choose one technique as the superior one. The choice for a spatial isolation mechanism depends on many factors, some of which depend on the application, such as the overhead that a particular mechanism imposes for a particular application. In addition, even for a given application, the choice for a spatial isolation mechanism may depend on external factors, for example the same application might be deployed in different environments with varying safety requirements or different degrees of electromagnetic interference (EMI). There may also be constellations where a combination of hardware- and software-based memory protection may be sensible or necessary to meet the given safety requirements. To determine the best-suited option for a given scenario, not only the qualitative aspects need to be considered but also the quantitative cost of the different alternatives. The evaluation of the quantitative cost is only feasible if switching between the alternatives is easily possible and can be performed for the cost determination.

The aim of this thesis is to design, implement and evaluate a framework for the

domain of safety-critical, deeply embedded systems that supports hardware-based memory protection using an MPU and software-based memory protection based on the type-safe language Java and a multi-JVM concept. The decision for these mechanisms is explained in Section 2.5. The framework achieves the following objectives:

- **Fine-Grained Configurability:** The framework allows selecting from hardware- and software-based memory protection without needing to change the code of the application, thereby allowing to easily switch to the best suited mechanism as the external requirements or the characteristics of the application change. This thesis also explores further graduations of the two mechanisms to allow a more fine-grained trade-off between cost and the degree of protection provided.

- **Mixed-Mode Operation:** To support the integration of applications with different characteristics while using the best-suited memory protection mechanism for each, the framework allows the coexistence and combination of different spatial isolation mechanisms in one system configuration.

- **Soft Migration:** A huge base of legacy code exists in the industry. Only a minor part of the application code is newly developed for a new product, most is reused from the existing code [48]. To make a transition to Java feasible, this thesis explores the typical properties of deeply embedded applications. The developed framework supports the reuse of portions of legacy code and the transition at a manageable level, although not all the benefits of the framework are available for legacy code parts.

- **Support Quantitative Evaluation:** To support the identification of the best-suited protection mechanism for a given application, the framework supports the evaluation of the cost imposed by each mechanism. This is implicitly enabled by the goal of configurability that easily allows switching between the mechanisms to measure the cost imposed by each.

#### 1.3 Broader Scope of this Work

Although the electronic control units in the automotive sector are used as a motivating example in the previous section, the work presented in this thesis applies to many other fields of embedded systems as well, whereby the market conditions and technical requirements may vary moderately between the different fields. Mixed-criticality systems where software components of differing safety-criticality are integrated on one system in a manner that does not require the non-safety relevant parts to be verified using the same time-consuming and costly processes as the safety-critical parts are an active research topic in other fields such as aerospace as well. In fact, later in this thesis an avionic application is used as a running example, mainly due to the lack of availability of an equally comprehensive automotive application. The used hardware and system software are the same as used in the automotive context, however, and the requirements of the application concerning resources and safety-criticality are equally – if not more – stringent, than that of a safety-critical automotive component.

#### 1.4 Structure of this Thesis

The remainder of this thesis is structured into the following chapters:

- **Chapter 2** presents and discusses properties of both hardware- and software-based techniques for establishing spatial isolation. The discussion is concluded by the choice of hardware-based protection using an MPU and software-based protection on the base of a multi-JVM, which show to be the most suited for the targeted domain of safety-critical embedded systems. In addition, Chapter 2 also reviews more broadly related approaches that aim at providing memory safety or spatial isolation with a focus on the domain of embedded devices.

- **Chapter 3** analyzes which properties of spatial isolation are required and which are not in the context of the safety-critical embedded field, and based on these properties develops a suitable application and isolation model that defines different levels of protection and lays the base for the developed framework. In addition, an example application is introduced that is consistently revisited throughout this thesis. Finally, I investigate how the two chosen isolation mechanisms map to that model.

- **Chapter 4** develops the design and architecture of the framework. The focus in this chapter is on the configurability that allows choosing between, mixing and combining the two chosen isolation mechanisms in a single system.

- **Chapter 5** studies the step-wise migration on the basis of components to the developed framework. To enable the interaction of legacy and migrated components, the most widely spread communication idioms found in legacy embedded code are identified and integrated into the framework.

- **Chapter 6** shows that the developed framework achieves the objective of allowing the easy and direct comparison of the cost imposed by the different isolation techniques by performing such a comparison at the example of the control software of a quadrotor helicopter. In addition, I evaluate quantitative aspects of the framework itself, including an evaluation of the overhead imposed by using Java as a language instead of C or C++ for the targeted type of embedded applications.

- **Chapter 7** wraps up the content of the thesis and concludes with the major findings and contributions of the presented work, and discusses possible directions for future work.

#### **1.5 Own Publications Related to this Thesis**

Parts of the ideas and results discussed in this thesis have previously been published. The following is a list of these publications:

- [114] M. Stilkerich, C. Wawersich, W. Schröder-Preikschat, A. Gal, and M. Franz. "OS-EK/VDX API for Java." In: Proceedings of the Linguistic Support for Modern Operating Systems ASPLOS XII Workshop (PLOS '06). (San Jose, CA, USA). New York, NY, USA: ACM Press, Oct. 2006, pp. 13–17. ISBN: 1-59593-577-0. DOI: 10.1145/1215995. 1215999

- [124] C. Wawersich, M. Stilkerich, and W. Schröder-Preikschat. "An OSEK/VDX-Based Multi-JVM for Automotive Appliances." In: *Embedded System Design: Topics, Techniques and Trends.* (Irvine, CA, USA). IFIP International Federation for Information Processing. Boston: Springer-Verlag, 2007, pp. 85–96. ISBN: 978-0-387-72257-3

- [111] M. Stilkerich, D. Lohmann, and W. Schröder-Preikschat. "Memory Protection at Option." In: Proceedings of the 1st Workshop on Critical Automotive Applications: Robustness & Safety. (Valencia, Spain). New York, NY, USA: ACM Press, 2010, pp. 17– 20. ISBN: 978-1-60558-915-2. DOI: 10.1145/1772643.1772649

- [110] M. Stilkerich, D. Lohmann, and W. Schröder-Preikschat. "Gradual Software-Based Memory Protection." In: Proceedings of the Workshop on Isolation and Integration for Dependable Systems (IIDS '10). (Paris, France). New York, NY, USA: ACM Press, 2010. ISBN: 978-1-4503-0120-6

- [119] I. Thomm, M. Stilkerich, C. Wawersich, and W. Schröder-Preikschat. "KESO: An Open-Source Multi-JVM for Deeply Embedded Systems." In: *JTRES '10: Proceedings* of the 8th International Workshop on Java Technologies for Real-Time and Embedded Systems. (Prague, Czech Republic). New York, NY, USA: ACM Press, 2010, pp. 109– 119. ISBN: 978-1-4503-0122-0. DOI: 10.1145/1850771.1850788

- [36] C. Erhardt, M. Stilkerich, D. Lohmann, and W. Schröder-Preikschat. "Exploiting Static Application Knowledge in a Java Compiler for Embedded Systems: A Case Study." In: JTRES '11: Proceedings of the 9th International Workshop on Java Technologies for Real-Time and Embedded Systems. (York, UK). New York, NY, USA: ACM Press, 2011, pp. 96–105. ISBN: 978-1-4503-0731-4. DOI: 10.1145/2043910.2043927

- [112] M. Stilkerich, J. Schedel, P. Ulbrich, W. Schröder-Preikschat, and D. Lohmann. "Escaping the Bonds of the Legacy: Step-Wise Migration to a Type-Safe Language in Safety-Critical Embedded Systems." In: Proceedings of the 14th IEEE International Symposium on Object-Oriented Real-Time Distributed Computing (ISORC '11). (Newport Beach, CA, USA). Ed. by G. Karsai, A. Polze, D.-H. Kim, and W. Steiner. IEEE Computer Society Press, Mar. 2011, pp. 163–170. ISBN: 978-0-7695-4368-0. DOI: 10.1109/ISORC.2011.29

- [118] I. Thomm, M. Stilkerich, R. Kapitza, D. Lohmann, and W. Schröder-Preikschat. "Automated Application of Fault Tolerance Mechanisms in a Component-Based System." In: JTRES '11: Proceedings of the 9th International Workshop on Java Technologies for Real-Time and Embedded Systems. (York, UK). New York, NY, USA: ACM Press, 2011, pp. 87–95. ISBN: 978-1-4503-0731-4. DOI: 10.1145/2043910.2043925

- [113] M. Stilkerich, I. Thomm, C. Wawersich, and W. Schröder-Preikschat. "Tailor-Made JVMs for Statically Configured Embedded Systems." In: *Concurrency and Computation:*

*Practice and Experience* 24.8 (2012), pp. 789–812. ISSN: 1532-0634. DOI: 10.1002/cpe. 1755

# 2 State of the Art

In this chapter, I present and discuss both established and academic techniques to achieve memory protection suitable for achieving fault-containment for memory access errors, and operating system architectures with protection facilities that build upon these mechanisms. Concluding the discussion, I select one hardware- and one software-based mechanism that I pursue further in this thesis.

#### 2.1 Levels of Memory Protection

Memory protection can be applied at different degrees. Two basic levels that can be distinguished are the sandboxed execution of untrusted code as opposed to the – potentially trusted – execution of memory-safe code.

#### 2.1.1 Sandboxing

The sandboxed execution of code focuses on faults in potentially untrusted code. Sandboxing does not detect semantic errors in the executed code, such as out-ofbounds array accesses (or, more generally, buffer overflows), use of uninitialized values, or accesses to dead stack frames, except where these accesses would impact other applications' data. What faults are detected by a sandboxing approach varies for different techniques. Some would, for example, detect memory access errors that address unused portions of the address space, whereas others would silently ignore the error. Another common trade-off is the detection of errors versus the simple masking. In the former case, a memory access outside the memory area of the sandboxed application raises an error, whereas in the latter case the sandbox merely ensures that such accesses cannot happen, for example by applying a bitmask to all memory addresses prior to dereferencing that ensures that the access is within the application memory. The basic guarantee common to all sandboxing approaches is that memory access errors of one software component do not affect the data of other software components, which is sufficient to provide spatial isolation.

#### 2.1.2 Memory Safety

As opposed to sandboxing, where executing the code in a controlled environment contains the defects of potentially untrusted code, memory safety is a property of code that guarantees that the code itself does not use memory in an unsafe way. The term *memory safety* has often been used in the literature without a uniform definition of the guarantees given by such code. One definition [3] given by Aiken, Fähndrich, Hawblitzel, Hunt, and Larus (Microsoft Research) in the context of the Singularity project is the following:

Memory safety ensures the validity of memory references by preventing null pointer references, references outside an array's bounds, or references to deallocated memory.

Other projects that define approaches to produce memory-safe code may vary in the safety properties provided. A common exclusion is the absence of references to deallocated memory (that is, dangling pointers/references). In the discussion of related approaches later in this chapter I point out what memory-safety properties a particular approach has.

Memory safety by itself does not provide strict spatial isolation and ensure the containment of logical faults, however, two memory-safe components can be spatially isolated by eliminating shared data, given that the memory safety is complete with respect to the above definition.

#### 2.1.3 Type Safety

A property at the level of the programming language that is closely related to memory safety is *type safety*. The same authors [3] as above define it as:

Type safety ensures that the only operations applied to a value are those defined for instances of its type.

Concerning the memory accesses of a program, type safety provides many of the properties of memory-safe code, for example, dangling references must not exist (or be used) in a type-safe program. While null pointer dereferences or out-of-bounds array accesses are commonly not considered to be type errors, these errors are practically avoided (or detected) by any type-safe programming language (or its runtime system). Thus in practice, the code generated from a program written in a type-safe language is also memory safe, even though most type-safe languages need to check for some error conditions at runtime.

#### 2.2 Comparison Criteria

In the following, I present both hardware- and software-based techniques to establish memory protection and review their suitability for use in the domain of deeply embedded, low-cost and real-time systems. My review takes the following criteria into account, which are discussed in detail in the text and summarized in Table 2.1 on page 32. For space reasons, the criteria are abbreviated in Table 2.1. The criteria are:

- **HW Req** Hardware requirements of the approach, by availability in typical microcontrollers for the target domain.

- $\oplus$  No special hardware needed

- Commonly available hardware needed

- $\ominus$  Hardly existent hardware needed

- **Flex** Flexibility and granularity of the protection, incorporating the size and provided maximum number of memory regions protected.

- $\oplus$  Granularity of language-level objects in sufficiently large numbers

- $\bigcirc$  Coarse-sized regions in sufficiently large numbers

- $\ominus$  Few, coarse-sized regions

- Leg Code Effort needed to adapt legacy code, which is assumed to be present in the form of C source code.

- $\oplus$  No modifications necessary

- $\bigcirc$  Moderate (up to 10 %) changes to existing code needed

- $\ominus$  Considerable code refactoring or rewriting required (exceeding 10 %)

- **Cost** Average cost in execution time or memory of using the protection approach in relation to a plain C application that executes fully privileged. The higher of the average CPU versus memory cost is considered.

- $\oplus$  Negligible (up to 10 %)

- $\bigcirc$  Moderate (up to 50 %)

- $\ominus$  Intolerable (exceeding 50 %)

This classification is based on the spectrum of the actually published overheads to provide a gross diversification. In cost-sensitive domains, added costs of up to 50 percent are considered intolerable as well.

- Fast IDC (Inter-Domain Communication) Supports fast communication among spatially isolated protection domains. Shared memory areas are excluded from this consideration, given that they present an exception to the isolation.

- $\checkmark\,$  Supports fast IDC

★ Does not support fast IDC

N/A Not applicable, or no numbers published

- **EMC** Robustness of the spatial isolation with respect to transient hardware faults, for example bit flips in memory caused by electromagnetic interference. Rating based on the protection-relevant context stored in memory.

- $\checkmark$  Negligible risk, only few words of protection context in memory

- ★ Considerable amount of protection-related context in memory

- **Prot Level** Level of protection provided, as discussed in Section 2.1

- **Pred** Predictability of the mechanism, assessing its suitability for the use in real-time systems. Based on whether the worst-case execution time of a program can differ heavily from the average caused by external factors such as the presence of other programs, particularly on the state of caches. Caches not related to memory protection are not considered, as these need to be incorporated independent of the protection technique.

- $\checkmark$  The execution time is mostly independent of that of other programs.

- ★ Predicting the worst-case execution time of a program under the respective protection approach either requires sophisticated analyses that are not commonly available or yields impractically high worst-case estimates.

- **CPU Prot** Whether the approach provides timing protection (that is, prevents monopolization of the CPU by one application)

- **TCB Size** Size of the code base that needs to be relied on for the protection to work correctly.

- $\oplus$  Simple mechanism, typical implementations less than 100 lines of code

- $\bigcirc$  Relies on a verifier that performs simple program analyses

- $\odot$  Requires the correct function of a full compiler or involves complex whole program analyses

It should be noted that Table 2.1 is only meant to provide a coarse overview. The ratings are not directly comparable for various reasons. Published results are based on different test or benchmarks applications, often rooted in diverse target domains and with differing characteristics. The coarse rating may also conceal large deviations, for example relative costs of 60 percent and 1000 percent are both equally rated as unacceptable. In few cases, no data is published for a particular criterion and the table instead contains a personal estimate based on data of similar approaches. Nevertheless, the overview should be sufficiently accurate to rate the various approaches.

#### 2.3 Hardware-Based Memory Protection Approaches

Hardware-based memory protection mechanisms build on special hardware mechanisms that check every memory access instruction for compliance with the memory protection policy enforced by the particular unit. Commonly, read, write and execution permissions can be granted for portions of the memory. While the way the memory is organized differs among the different approaches, there are some similarities common to all implementations.

Although the memory accesses are fully checked by the hardware, software is always needed that configures the protection hardware in a way that sets up the appropriate memory access permissions for the currently executing code. This software is part of the operating system. For the protection to be effective, the application that is subject to memory protection should not be able to change the configuration of the protection hardware<sup>1</sup>. The code responsible for managing the protection hardware thus needs to be granted additional access privileges compared to the regular application code. A processor that is equipped with memory protection hardware therefore needs to provide at least two privilege levels, often referred to as the supervisor mode and the user mode of the execution. Only code executing in supervisor mode is allowed to modify the configuration of the protection hardware. In addition, the processor needs an exception mechanism that can be used by the protection hardware to signal violations of the configured protection concept, such as the attempt to execute a privileged instruction from user mode or a memory access that violates the setup protection, and enables handling of such error conditions by the privileged memory management software. Finally, a mechanism for the controlled transition between the privilege levels is needed. For the latter, most processors provide a distinct supervisor *call* instruction that raises a special exception and transfers control to the operating system.

#### 2.3.1 Coarse-Grained Approaches Without In-Memory Data Structures

#### 2.3.1.1 Region-Based Memory Protection Unit

A memory protection unit (MPU) establishes range-based memory protection. The basic principle is that a number of address ranges (regions) of the physical address space can be assigned particular access rights. Memory accesses are only allowed to the defined regions with permissions appropriate for the respective access. Despite sharing this simple principle, concrete implementations differ. For example, the heterogeneous MPU of the Infineon Tricore TC1796 microcontroller provides two sets of region registers, with two code and four data regions each. Execute permissions can be granted only on code regions, whereas read and write permissions are only available for data regions. If multiple overlapping regions contain an address, the combined

<sup>&</sup>lt;sup>1</sup>Some approaches that target trusted – but potentially buggy applications – do deliberately not prevent the applications from modifying the protection hardware, trading improved efficiency for a slightly increased risk of memory corruption.

rights of all involved regions are effective for the address. The optional MPU of ARM Cortex-M3 processors is a homogenous MPU that supports eight regions usable for both code and data. However, whereas the Tricore's MPU allows defining regions for arbitrary ranges, the MPU of the Cortex-M3 requires regions to be of a size that is a power of two with a minimum size of 32, and the start address of the region to be aligned to its size. For overlapping regions, rights do not accumulate but the regions are ordered and the first matching region according to that order is effective.

#### 2.3.1.2 Segmented Memory

Segmented memory is similar to the region-based protection using an MPU in that each segment is defined by a base address, a length and access rights, but segmented memory additionally involves address translation. The hardware unit is called a memory management unit (MMU) and may provide additional memory management functionality beyond the scope of protection. The addresses used by the program are offsets into a particular segment. On address translation, the offset is checked against the segment's length and the permissions of the segment are checked with the type of memory access. If both tests succeed, the offset is added to the segment's base address to determine the physical memory address. In addition to the direct translation, segmented memory can also be combined with paged memory.

#### 2.3.2 Caching Approaches with In-Memory Data Structures

#### 2.3.2.1 Page-Based Memory Management Unit

In a page-based memory organization, the address space is organized in pages of a fixed size. Typical page sizes are in the range of 1–64 KiB. As with segmented memory, the hardware unit is called an MMU and provides additional, non-protection related functionality. The most notable one is address translation on a per-page basis. The address mapping is defined in the page table, an in-memory data structure that contains the physical address and permissions for each page, and possibly additional attributes not related to memory protection. Commonly, a multi-level page table is used to reduce the size of the page table. A page table is defined for each protection realm. To avoid expensive memory lookups in the page table on each memory access, the MMU is equipped with a fast, fully-associative cache that holds recently used page table entries, the *translation look-aside buffer (TLB)*. Typical TLB sizes are in the range of up to 1024 entries. The optional MMU in the Tricore architecture specifies a TLB with a capacity of 4–128 entries. Some MMUs handle a TLB miss and the following page-table lookup in hardware (for example, x86), whereas others (for example, Tricore) leave the management of the TLB to the operating system.

#### 2.3.2.2 Mondrian Memory Protection

Mondrian [126] memory protection (MMP) is a hardware implementation that allows defining memory access permissions at the granularity of single memory words. MMP

supports an arbitrary number of segments of variable length for that permissions can be specified. The central data structure used by MMP is the *permission table*, comparable to the page table used in page-based memory management, but restricted to only contain protection-related data. Mondrian uses a two-stage cache concept: At the first level, a so-called side-car register accompanies each of the processor's address registers. The side-car register caches the access permissions for the segment used in the last memory access addressed using the respective address register. The second level is the *permissions lookaside buffer* that caches entries of the permission table similar to the TLB in MMU implementations, with a typical capacity of 64 or 128 entries. Based on Mondrian is Mondrix [127], a variant of the Linux kernel that uses Mondrian to isolate kernel modules. Mondrian has so far only been implemented and evaluated in simulators. For Mondrix, a modified version of the Bochs x86 simulator was used.

#### 2.3.2.3 UMPU: Software-Fault Isolation in Hardware

Kumar et al. presented a hardware extension [66] called UMPU to an AVR ATmega103 8-bit microcontroller that implements the runtime checks required for a software-based fault isolation approach (Section 2.4.1.1), specifically Harbor [65], in hardware. The mechanism supports one trusted and up to seven untrusted protection domains. A part of the memory is reserved for the use by the untrusted domains and organized in blocks of a fixed, configurable size. The authors used a block size of eight bytes in their experiments. For each of these blocks, the domain ownership is tracked in the *memory map*, an in-memory data structure containing four bits for each block. To provide fault containment of memory access errors, the **store** instruction of the processor is extended to check in the memory map whether the accessed block belongs to the currently active domain, which is tracked in a separate processor register. To enable inter-domain communication, each domain can statically export a jump table of code entry points in a designated flash page. When another domain calls one of the exported functions through the jump table, the active protection domain is changed to that of the exporting domain and execution continues at the exported entry point. Upon return, the previous domain is restored. For this, the call and return instructions of the architecture have been modified. A single runtime stack is used for all domains. The stack resides in a memory area that is not in the range managed by the memory map. To avoid stack corruptions among domains, a separate stack bound register is used, that contains the current lower limit of the upward-growing stack. This bound is updated in the call and return instructions, and inspected by the store instruction to avoid stack corruption. Return addresses are managed on a separate safe stack to provide control flow integrity [1].

It is not entirely clear what happens if an illegal store operation is encountered. This is an interesting issue as the AVR architecture does not provide a mechanism for the processor to signal synchronous exceptions. The published text [66] suggests that such illegal writes are simply not performed without signaling the exception condition.

#### 2.3.2.4 HardBound

HardBound [33] is a hardware extension to directly support fat pointers in the processor. A fat pointer is a pointer enriched by the base address and the bounds of the referenced object. HardBound is an academic project and has been evaluated by extending the Simics [73] full system simulation of an x86 processor. The processor is extended by a new unprivileged instruction setbound, which can be used to define the base address and bounds information for an address stored in a register. The processor subsequently checks all memory accesses to be within the bounds of the used pointer. HardBound is a mechanism that works at the user-level and is not sufficient for providing spatial isolation, as it does not provide full memory safety as defined above (in particular, it is only safe in the absence of dangling pointers).

To store the bounds information for an address, HardBound uses two in-memory data structures. The *shadow space* stores the base and bounds information for an address in a separate memory region to retain the internal pointer representation for compatibility reasons. The location where the base and bounds information for an address are stored can be computed from the address value. HardBound assumes a page-based address management that allocates pages for the shadow space on demand. To avoid the allocation of a shadow space twice the size of the program's data space, HardBound manages a second in-memory data structure that contains a bit for each memory word to mark whether the word contains a pointer, or not, the *tag metadata space*. Fat pointer metadata in the shadow space is only allocated for pointers.

The fat pointer's meta data not only needs to be accessed for every load or store instruction, but also for many other CPU instructions to correctly propagate the bounds information, for example in addition or subtraction instructions for supporting pointer arithmetic. To reduce the number of memory accesses, HardBound implements an additional first level cache, the *tag metadata cache*, to cache blocks of the tag space. To further reduce the size of the shadow space, the authors present various alternative approaches to compressed pointers, encoding bounds information for common object in additional bits in the tag metadata space or unused bits in the pointer value itself.

The software must properly initialize the bounds information. In their experiments, the authors of HardBound extended the C library's dynamic allocation function malloc() to properly set the bounds information. For statically allocated objects and stack objects, a C compiler was modified to initialize the bounds whenever a pointer to such an object is created. Propagation of the bounds information when passing the pointer or doing pointer arithmetic is completely handled by the processor. The authors performed an evaluation by counting the micro operations performed by the CPU with and without the HardBound extension. The runtime overhead for a benchmark suite is five to nine percent on average for different variants of compressed pointers, with peaks of up to 23 percent for some applications. These numbers assume that bound checking can be implemented in hardware without increasing the time required for the affected processor instructions. An additional evaluation that counts an additional micro operation for each bound check of an uncompressed pointer increases the average runtime overhead by three to ten percent. The memory overhead

was compared by counting the number of pages allocated for the application. The average overhead of additionally allocated pages is from ten to 55 percent on average for different compression schemes, with up to 200 percent for some applications.

#### 2.3.3 Discussion

None of the academic approaches is built into a commercially available processor. MMUs are rarely found in embedded processors. Of the Tricore family, only the TC1130 is equipped with an MMU [77]. The reasons are manifold: The MMU in the ARM7TDMI processor increases its area tenfold and its power consumption twofold [66]. The comprehensive in-memory data structures that hold the memory access permissions result in vulnerability with respect to transient hardware errors that can break address mappings and permissions. The cache used to achieve acceptable runtime cost impairs the predictability and worst-case execution time analysis cannot predict the cache states in the presence of multiple threads. Assuming a cache miss on every memory access is impractically pessimistic. A case study [52] that investigates several MMU designs finds that the overhead to the virtual memory system is in the range of ten to 30 percent. The published runtime overheads for the scientific approaches are in the same range. The in-memory data structures also add to the memory footprint of the program, the more the finer the granularity of protection. For HardBound, the reported memory overheads are up to 200 percent. It should be noted that of the scientific approaches only UMPU was designed for the embedded domain, albeit not for real-time applications.

From all hardware protection units, MPUs are the most common in processors for the deeply embedded and real-time systems for their simple design and predictable runtime behavior. Nevertheless, as outlined in Section 1.2, MPUs are not available in the low-cost segments of microcontroller product lines. The limited number of regions constrains the flexibility and may not be sufficient for all applications, especially if the operating system grants temporary access to some memory areas in the course of inter-domain communication such as messaging. The application needs to organize its data physically grouped in memory to achieve a small number of memory regions, which may require changes to legacy applications. The small number of regions may also impair the ability to use special memory types (for example, fast but small on-chip memory versus slower but larger external memory) for parts of its data if that required an additional region that may not be representable in a static MPU configuration. Execution time overhead occurs when the protection realm needs to be changed, that is, when communicating with another software component or when invoking a system call. The mechanism may therefore be expensive for communication-intensive applications. Concerning the robustness with respect to transient hardware faults (bit-flips), MPU protection is robust as the protection registers are normally hardened against radiation. While the region settings for inactive tasks are stored as part of the task context in RAM and thus subject to transient faults, the statistical risk of a bit flip affecting a saved protection context is low and acceptable. MPU protection does not introduce any source of indeterministic behavior and is thus suitable for the

Figure 2.1: Levels at the Software-Based Memory Protection Mechanisms Take Effect

use in real-time settings. An operating system can virtualize the MPU, simulating an MPU with an (almost) arbitrary number of regions, which is for example done by Hightec's PXROS-HR operating system, allowing a more flexible MPU use by the application. This virtualization comes at the price of reduced predictability and potentially high overhead for certain usage patterns that collide with the operating system's region replacement strategy.

In a nutshell, MPUs are the only hardware memory protection units that are reasonably available in low-cost microcontrollers. This is for good reasons, as MPUs provide low-cost and low-overhead memory protection that is suited for cost-sensitive markets. The simplistic design and the robustness with respect to transient hardware faults make MPU-based protection easily verifiable and therefore a good choice for safety-critical applications. Finally, the absence of caches and in-memory data structures results in deterministic behavior that does not increase the complexity of worst-case execution time analysis, thus MPUs meet the requirements of real-time applications.

#### 2.4 Software-Based Memory Protection Approaches

Software-based approaches provide memory-safe code to varying degrees without requiring a hardware protection unit. The available software-based approaches are manifold. Many approaches build on the same underlying concept, however. The approaches can coarsely be classified by the level at that they provide memory safety. Figure 2.1 shows these levels: Language-level approaches build on a safe programming language that constructively provides memory safety at the source code level. Following in the code generation process is one or more compilation processes. Compiler-level approaches work on the intermediate representation of the compiler and analyze and transform it in such a way that the output of the transformation is memory

safe. Though working on the compiler's intermediate representation is theoretically independent of the source-level programming language, the transformations commonly assume certain properties that are implied by properties of the programming language, or place other restrictions on the input code. The transformation may fail with the rejection of the program if these expected preconditions are not met, or the analysis fails to prove that the input meets the expected constraints. At the final stage, a binary image containing executable machine code of the target instruction-set architecture (ISA) is produced. ISA-level approaches transform a binary image in a way that ensures memory safety.

The lower the level an approach hooks in the more general it can be applied. While language-based approaches mandate the use of a particular programming language, compiler-level approaches only require the use of a special compiler and binary-level approaches are theoretically entirely independent of the used language and toolchain. On the other hand, as source code is transformed to machine code, with each step down the toolchain information is lost and fewer assumptions can be made on properties of the program code without limiting generality. In the remainder of this section, I discuss software-based approaches categorized by these three levels, starting bottom up with binary level approaches.

# 2.4.1 Instruction-Set-Architecture-Level Approaches

#### 2.4.1.1 Software-Based Fault Isolation

Software-based fault isolation (SFI) [122] provides sandboxing of application modules by patching the binary code so that all critical machine instructions are replaced by a more elaborate routine that checks whether the operation complies with the guaranteed safety model before executing it. The original approach aimed at isolating closely coupled software modules for which hardware-based memory protection incurred too high cost, caused by the context switching overhead in frequent communication between modules, for the example the sandboxed execution of third-party program plugins. The common concept is that each isolated entity has own code and data segments, and each critical operation (for example, store, jump) is patched to a checked version.

The original implementation by Wahbe et al. [122] is actually a compiler approach, as their prototype has been implemented by modifying the GCC compiler and therefore benefits from extended code transformation capabilities available at that stage. The motivation of the original approach is not to avoid the need for a hardware unit but to avoid the communication cost implied by using it. Two mechanisms are discussed: Segment matching detects faulty memory accesses by preceding each critical operation with a check for the address. The implementation requires four reserved registers that are not used by the normal application code and therefore a modified compiler. Sandboxing only ensures that the target memory location is within the segment of the running module by inserting code that patches the upper address bits to point to the segment but without checking it, requiring only two dedicated registers. In the embedded systems context, particularly the wireless sensor networks (WSN) community has picked up SFI as a research topic. WSN nodes are typically equipped with very small (for example, AVR 8-bit) microcontrollers that provide no hardware support for memory protection or unprivileged execution modes.