# **DIY – Individual Prototyping and Systems Engineering**

**Max Gaukler**

Lehrstuhl für Regelungstechnik

Sommersemester 2019

# DIY – Individual Prototyping and Systems Engineering

Entwurf und Fertigung von elektronischen Schaltungen

**Max Gaukler**

Lehrstuhl für Regelungstechnik

Sommersemester 2019

- Umsetzung einer Idee in eine elektronische Schaltung:

- 1 Konzeptfindung → Vorlesung „Elektronik“

- 2 Schaltplan

- 3 Auswahl der Baugrößen

- 4 Platinenlayout

- 5 Platinenfertigung

- 6 Bestückung

- Heutige Vorlesung: vom Papier-Schaltplan bis zur fertigen Platine

- Schwerpunkt: einfache Schaltungen, Fertigung im Hobbymaßstab

## 1 Einleitung

## 2 Grundlagen

- Aufbautechnik

- Platinenfertigung

## 3 Rechnergestützer Entwurf

- Schaltplan

- Platinenlayout

# Platine

- Leiterplatte (Platine) (engl. *printed circuit board, PCB*): Kupferbahnen auf Isolator

- aufgelötete Bauelemente

- Verbindungen gemäß Schaltplan

Bild: <https://commons.wikimedia.org/wiki/File:lccd-angle-back.jpg>, Autor: Murray 1010 via Wikimedia Commons,

Lizenz: CC-BY-SA 3.0

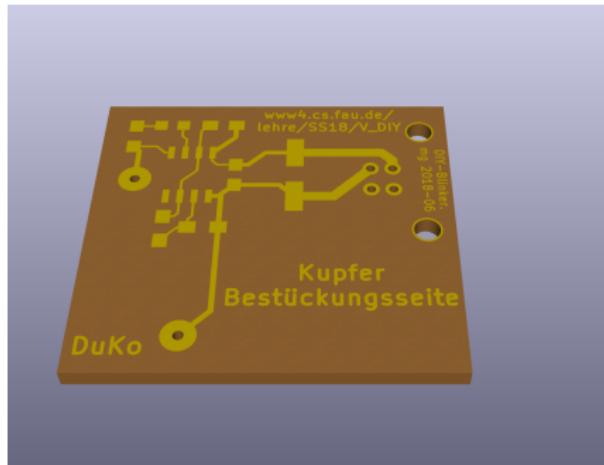

# Platine: Aufbau

- GFK-Basismaterial (GlasFaserverstärkter Kunststoff)

- Bohrlöcher

- 1 – 8 Kupferlagen (Leiterbahnen)

- unten: „Lötseite“

- oben: „Bestückungsseite“

- ggf. weitere Innenlagen (teuer)

- Durchkontaktierungen

(engl. *vias*)

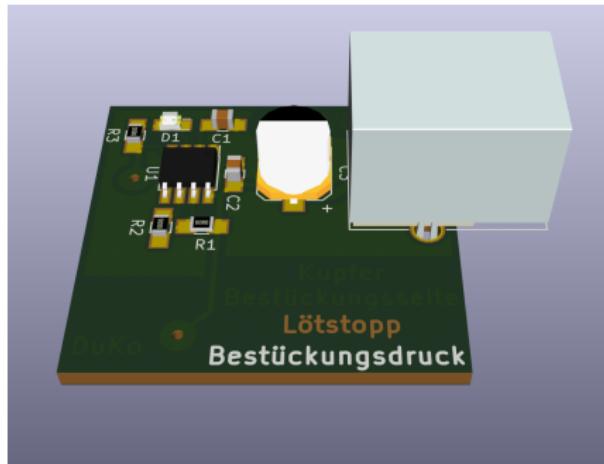

- Lötstopplack (engl. *stopmask*)

- Bestückungsdruck („Siebdruck“)

(engl. *silkscreen*) (meist nur auf Bestückungsseite)

- Bauteile (industrielle Bestückung: möglichst nur auf Bestückungsseite; einlagige Platine: SMD auf Lötseite, THT auf Bestückungsseite)

# Platine: Aufbau

- GFK-Basismaterial (GlasFaserverstärkter Kunststoff)

- Bohrlöcher

- 1 – 8 Kupferlagen (Leiterbahnen)

- unten: „Lötseite“

- oben: „Bestückungsseite“

- ggf. weitere Innenlagen (teuer)

- Durchkontaktierungen

(engl. *vias*)

- Lötstopplack (engl. *stopmask*)

- Bestückungsdruck („Siebdruck“)

(engl. *silkscreen*) (meist nur auf Bestückungsseite)

- Bauteile (industrielle Bestückung: möglichst nur auf Bestückungsseite; einlagige Platine: SMD auf Lötseite, THT auf Bestückungsseite)

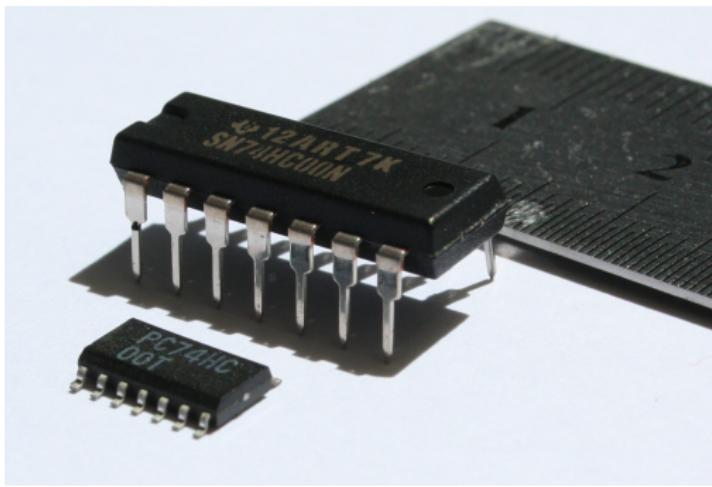

# Aufbautechniken: SMD versus THT

- THT: Durchsteckmontage (engl. *through-hole technology*)

Bauteil wird in Bohrloch gesteckt und rückseitig verlötet. Eher veraltet.

- SMD: oberflächenmontiertes Bauteil (engl. *surface-mounted device*)

wird aufgelötet, sehr platzsparend, teilweise nicht mehr Hobby-geeignet

Bild: SMD- (unten) und THT-Variante (oben) des gleichen Chips 74HC00.

[https://commons.wikimedia.org/wiki/File:Logic\\_ICs\\_in\\_size\\_comparison.JPG](https://commons.wikimedia.org/wiki/File:Logic_ICs_in_size_comparison.JPG),

Autor: Sundance Raphael via Wikimedia Commons, Lizenz CC-BY-SA 3.0

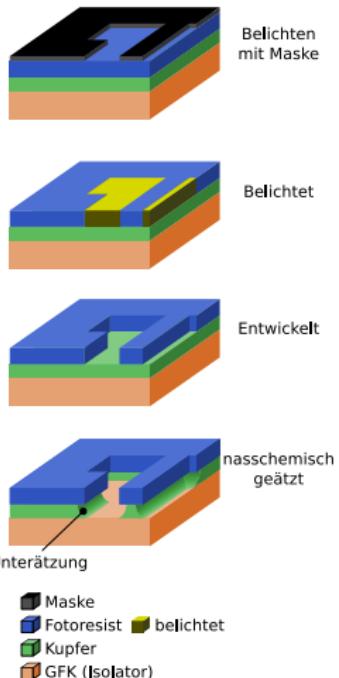

# Photochemische Platinenfertigung im Hobbymaßstab

- 1 Rohmaterial: GFK mit Kupfer und Fotolack

- 2 Zusägen und entgraten

- 3 Schutzfolie entfernen

- 4 **Belichten** mit Maske (ausgedrucktes Layout)

- 5 **Entwickeln**: Belichteten Fotolack entfernen

- 6 **Ätzen**: Freigelegte Metallstellen entfernen

- 7 Bohren

- 8 Entschichten<sup>1</sup>: Unbelichteten Fotolack entfernen

- 9 optional: Durchkontaktierungen einpressen

- 10 optional: Verzinnen gegen Korrosion

Bild abgewandelt von: [https://commons.wikimedia.org/wiki/File:Etching\\_wet-chemical\\_vs\\_rie\\_\(DE\).svg](https://commons.wikimedia.org/wiki/File:Etching_wet-chemical_vs_rie_(DE).svg)

Autor: Cepheiden via Wikimedia Commons, Lizenz CC-BY-SA 3.0

<sup>1</sup>nach dem Bohren, um Verschmutzung zu verringern

- 1 Ausgangspunkt: nackte (oder dünn verkupferte) GFK-Platte

- 2 Bohren

- 3 **Verkupfern** (Löcher durchkontaktieren)

- 4 Fotolack aufbringen

- 5 **Belichten, Entwickeln, Ätzen, Entschichten**

- 6 optional: Lötstopplack und Bestückungsdruck

- 7 optional: Verzinnen oder Vergolden

- 8 optional: E-Test (Kurzschlüsse, Unterbrechungen)

Selber fertigen ist äußerst unüblich!

Üblicherweise werden Platinen nur durch externe Auftragsfertiger gefertigt, für 10x16 cm doppelseitig kostet dies ca. 60 Euro (Fernost: ca. 20 Euro).<sup>2</sup>

<sup>2</sup><https://www.mikrocontroller.net/articles/Platinenhersteller>

## 1 Einleitung

## 2 Grundlagen

- Aufbautechnik

- Platinenfertigung

## 3 Rechnergestützer Entwurf

- Schaltplan

- Platinenlayout

# Wiederholung: Schaltungsfindung

Zuerst überlegen, was und wie man will, nicht einfach drauflosarbeiten!

## Mögliche Quellen für Entwürfe:

- **Selber entwerfen**, systematisches Kombinieren von Grundschaltungen (ggf. hoher Aufwand)

- **Datenblätter** interessanter Bauteile

- **Application Notes** (Kochrezepte mit meist hoher Qualität)

- Anleitungen aus der Literatur (mit etwas Vorsicht)

- Projekte anderer im Internet (mit großer Vorsicht)

Es bleibt die Abwägung: Will ich mit hohem Aufwand „selber kochen“ oder schlechte „Fastfood-Qualität“ riskieren?

*Die Summe allen Übels ist stets gleich. — alte Ingenieursweisheit*

- Programme zur Schaltplan- und Platinenerstellung

- Im Hobbybereich geeignet:

- **KiCAD (umfangreich, Open Source)**

- Eagle (kostenlose Variante nur nichtkommerziell und eingeschränkt)

- DesignSpark PCB (nur unter Windows)

- Fritzing (Open Source, extrem eingeschränkt, nur für „Steckbrett-Basteleien“)

*Fritzing is a terrible tool that you should not use. — Brian Benchoff*

- Premium-Produkte z.B. Altium (kostet etwa 10k€, dafür extrem gut)

- Bedienung sehr unterschiedlich, Geschmacks- und Gewöhnungssache!

- Beschränkung der Vorlesung/Übung auf KiCAD: keine Lizenzeinschränkungen, Profi-Features (z. B. interaktives Routing), Workflow ähnlich zu Profi-Programmen

# Schaltplan erstellen

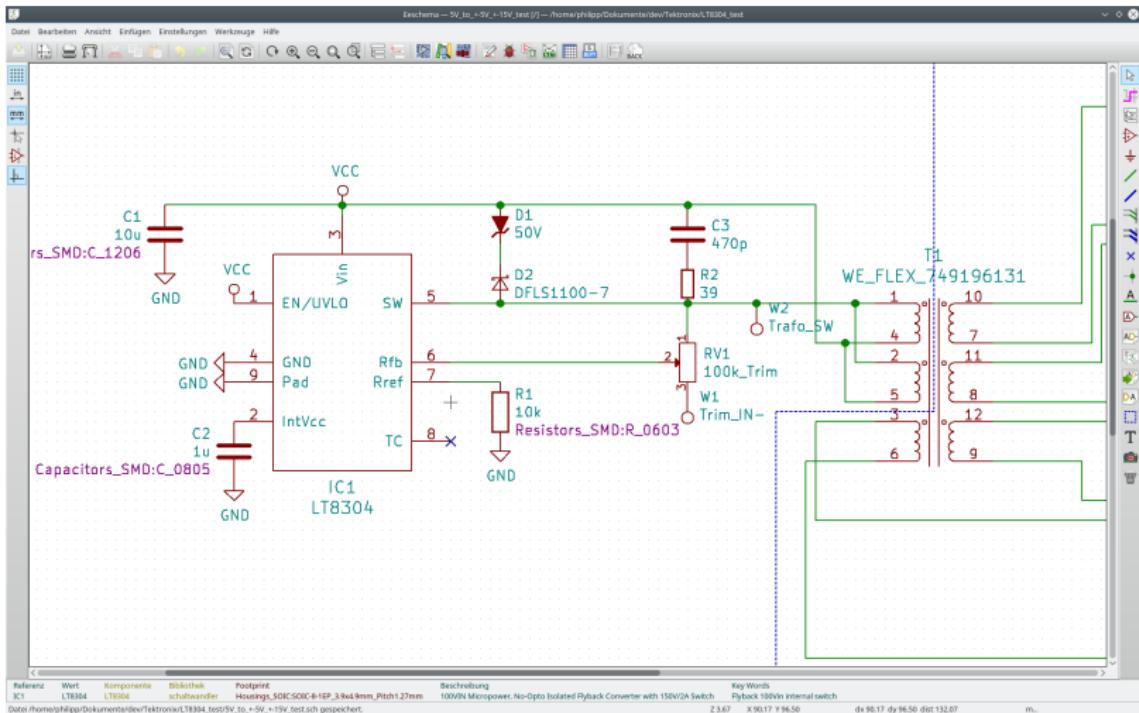

Abbildung: Schaltplan eines isolierten DCDC-Konverters

Ein Schaltplan soll **lesbar und übersichtlich** die Schaltung erklären.

Er ist **kein 1:1-Bild** der Verkabelung (Stromlaufplan)!

## Gute Praxis:

- Labels, besonders für Spannungsquellen und Masse

- wichtige Signale benennen, damit Name im Platinenlayout angezeigt wird

- Richtung, soweit sinnvoll möglich:

- Stromfluss von oben (+) nach unten (-)

- Signalfluss von links (Eingang) nach rechts (Ausgang)

- Nicht „stopfen“! Lieber Seitengröße erhöhen oder neue Seite hinzufügen.

- Kommentare für Besonderheiten, Entscheidungsgründe, ...

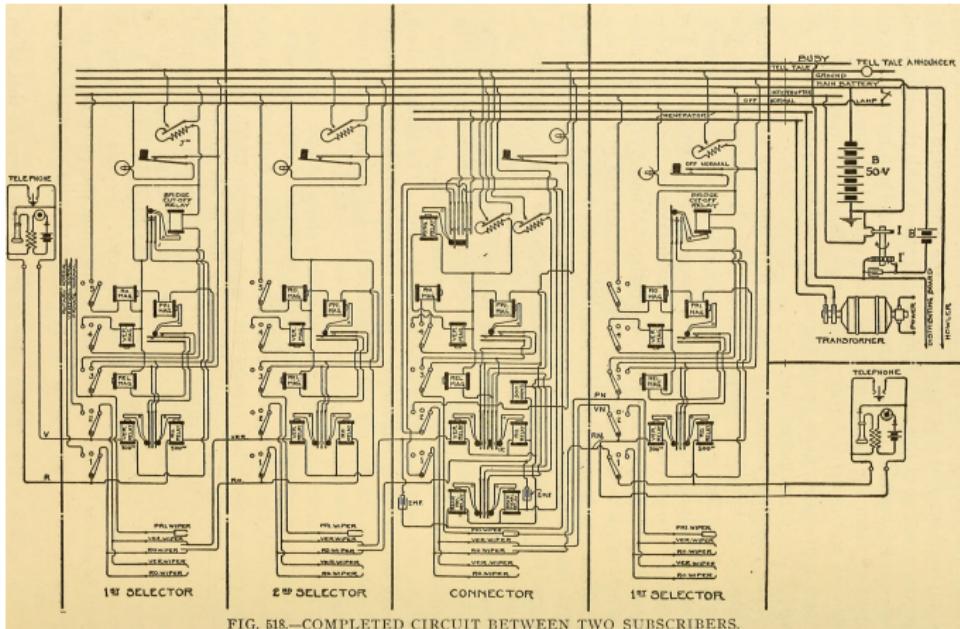

# Stromlaufplan – kein guter Schaltplan!

**Abbildung:** Stromlaufplan einer Telefonanlage (1905).

Kempster B. Miller, via Wikimedia Commons, Copyright abgelaufen.

[https://commons.wikimedia.org/wiki/File:American\\_telephone\\_practice\\_\(1905\)\\_-\\_14756423865.jpg](https://commons.wikimedia.org/wiki/File:American_telephone_practice_(1905)_-_14756423865.jpg)

Leitungen im Schaltplan sind ideal definiert, das heißt:

- Keine Innenwiderstände

- Keine Abstrahlung oder Kopplung zwischen Leitungen

- Keine Laufzeiten über Wegstrecken

Dies muss später beim Platinenlayout bedacht werden!

# Electric Rules Check (ERC)

ERC prüft den fertigen Schaltplan auf offensichtliche Fehler, etwa

- Spannungs-Ausgänge (z. B. 12V und 5V) miteinander verbunden

- Spannungs-Eingänge nicht mit einem -Ausgang verbunden

- Nicht verbundene Pins

- zum Teil Fehlalarme

## Tip: Gängige ERC-Fehler in KiCAD beheben

- Bauteil PWR\_FLAG um einen Anschluss (z.B. Stecker) künstlich als Versorgungsspannungs-Eingang zu markieren

- NoConn-Markierung () um einen Pin als nicht angeschlossen zu kennzeichnen

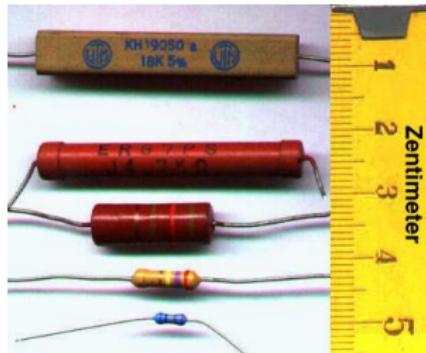

# Auswahl der Gehäuseform (engl. footprint)

Der Schaltplan enthält Symbole, z.B. einen Widerstand mit 100 Ohm.

Diese Bauteile gibt es aber in verschiedenen Baugrößen!

Welche Baugröße soll ausgewählt werden? Zu bedenken:

- Welche Leistung fällt an dem Widerstand ab?

- Welche Spannung muss er aushalten?

- Was ist die kleinste Bauform, die noch einfach zu löten ist?

- Wie fein kann ich die Platine fertigen?

Bild: Honina, Deutsche Wikipedia, Lizenz: GFDL, <https://commons.wikimedia.org/wiki/File:Widerst%C3%A4nde.JPG>

# Übergang vom Schaltplan zum Platinenlayout

- 1 Bauteile benennen (KiCAD: „Annotieren“)

- 2 Den Bauteilen (Symbole im Schaltplan) Gehäuseformen zuordnen

- *heavy symbols* (EAGLE): **Feste Zuordnung** beim Einfügen in den Schaltplan.

↳ Nachträgliche Änderung erfordert meist Löschen des Bauteils.

- *light symbols*: Flexible Zuordnung **nach** (teils: während) der Schaltplanerstellung.

↳ Funktioniert nicht wirklich, wenn je nach Bauform Pins unterschiedlich nummeriert sind oder gar fehlen.

- oft Mischung beider Konzepte: KiCAD eher „light“, aber z. T. unterschiedliche Symbole je nach Pinbelegung (Transistor: BCE, EBC oder CBE)

- 3 Netzliste exportieren und in Platinen-Editor importieren

- Maschinenlesbare Form des Schaltplans

- Netz: Gruppe miteinander verbundener Pins

passiert je nach Software automatisch

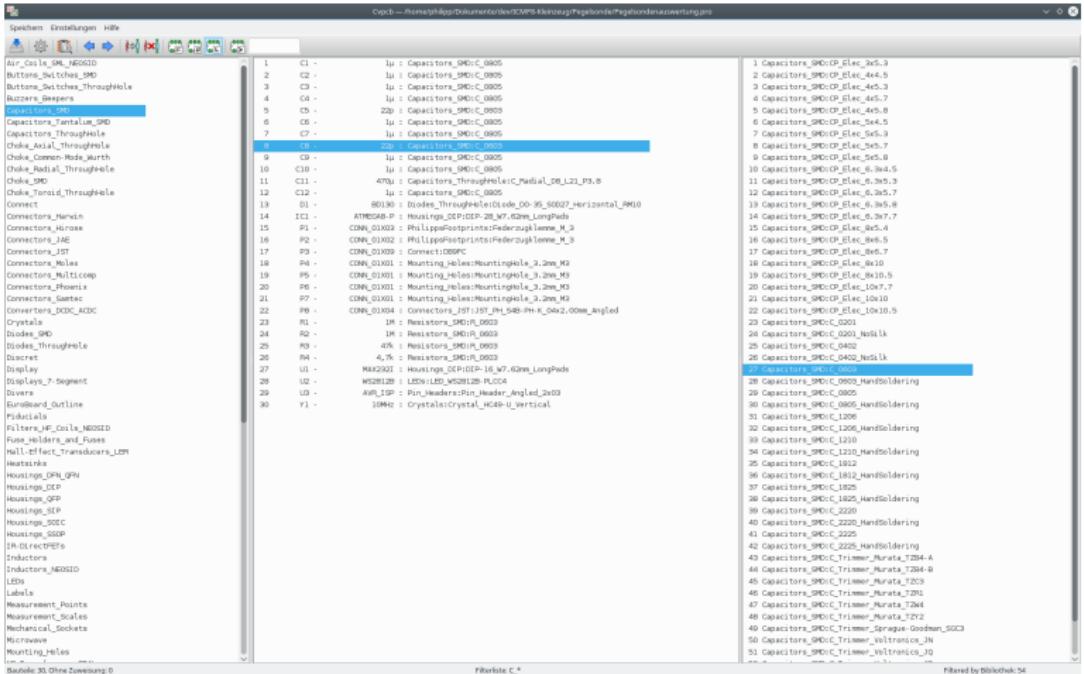

# KiCAD: Cvpcb – Zuordnung von Symbol und Bauform

Abbildung: Cvpcb aus der KiCAD-EDA-Suite

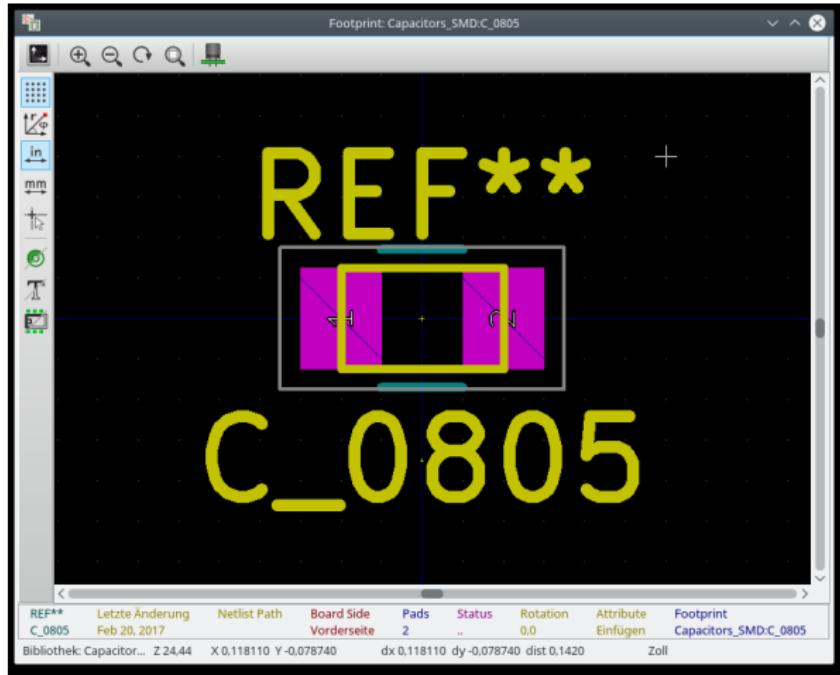

# Bauform-(Footprint)-Anzeige

Abbildung: 2D-Vorschau der Bauform im Platinenlayout-Programm

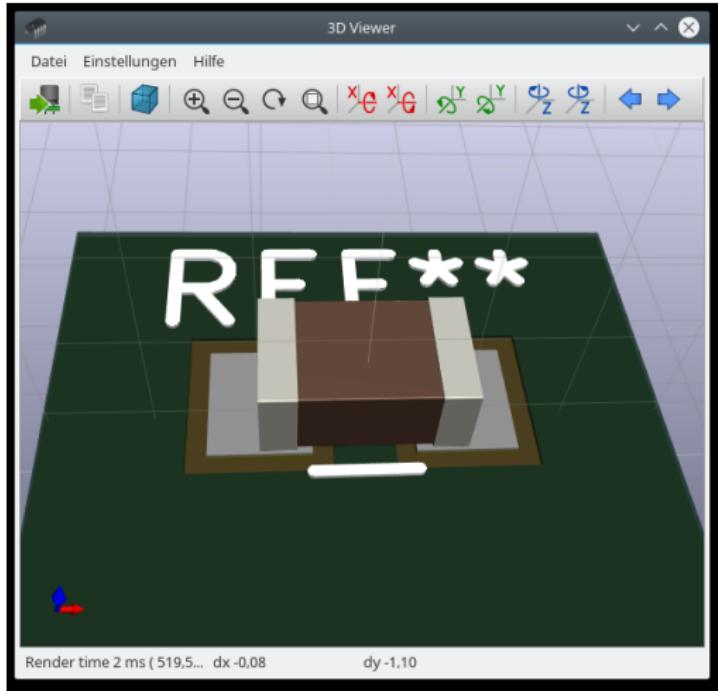

# Footprint-3D-Anzeige

Abbildung: 3D-Modell des Bauteils auf der Platine

## Achtung: Fehlerquelle

---

*Bitte immer alles richtig machen!*

Falsche Bauteilmaße oder Pin-Zuordnungen sind ein häufiger Fehler.

- Besonders bei SMD im Zweifel nachmessen oder im Datenblatt prüfen

- Zum groben Prüfen: Platine 1:1 ausdrucken und Bauteil draufsetzen

- Bauformen sind je nach Hersteller unterschiedlich bezeichnet

- Bei echten „light symbols“ (früher bei KiCAD) gibt es für *eine* Bauform *mehrere* Footprint-Einträge mit unterschiedlicher Pin-Bezeichnung (z.B. für Transistor mit B,C,E anstatt 1,2,3).

## Voreinstellungen:

- häufig gebrauchte Leiterbahnbreiten

- sinnvolle Durchkontaktierungsmaße

## Design-Regeln:

- Mindestabstand zwischen Leiterbahnen

- Mindestbreite der Leiterbahnen

- Minimaler Bohrlochdurchmesser

- Mindestgröße der Durchkontaktierungen

- ...

entsprechend der Fertigungsgrenzen (professionell oder im FabLab?)

# Einschränkungen der Hobby-Fertigung

- Mindestabstände und -breiten deutlich größer

- Durchkontaktierungen problematisch

- eingepresste DuKos unzuverlässig

- eingelötete Drahtstifte umständlich

- ⇒ so wenig DuKos wie möglich, lieber nur einseitig

- maximal zweilagig, besser einlagig

- Drahtbrücken als Ersatz für weitere Lagen

(im Layout-Programm wie eine weitere Lage eingeben)

- Bohrlöcher sind nicht durchmetallisiert, können nicht als Durchkontaktierung mitverwendet werden!

- Platinen für die Hobbyfertigung lassen sich meist ohne Änderungen professionell herstellen, weil sie für die maschinelle Fertigung sehr anspruchslos sind!

# Design-Regeln: Übliche Werte

Werte für geringes Risiko im FabLab / Standardpreis in der Industrie:

|                                         | FabLab <sup>3</sup> | Industrie <sup>4</sup> |

|-----------------------------------------|---------------------|------------------------|

| Abmessungen (max.)                      | 160x100             | 500x400                |

| Leiterbahnbreite<br>und -Abstand (min.) | 0,25 <sup>5</sup>   | 0,15                   |

| Ø Bohrloch (min.)                       | ca. 0,50            | 0,25                   |

| Ø Bohrloch (max.)                       | 3,00                | ∞                      |

| Ø DuKo Bohrung                          | =0,90               | ≥0,25                  |

| Ø DuKo Pad (min.)                       | 2,50                | Bohrung + 0,25         |

Alle Angaben in mm.

Weitere übliche Einheit: 1 mil = 1/1000 inch = 0,0254 mm

---

<sup>3</sup><https://fablab.fau.de/tool/platinenfertigung/>

<sup>4</sup><https://www.eurocircuits.de/leiterplatten-design-guidelines/>, Class 6 (Normalpreis)

<sup>5</sup>ist für SMD manchmal zu grob; mit Vorsicht ist auch noch 0,20 mm praktikabel

## Bauteile platzieren: Laden der Netzliste

- Jetzt kann die Netzliste geladen werden. Dabei werden neue Bauteile eingefügt, zunächst an willkürlichem Ort.

- Auch bei Veränderungen im Schaltplan muss dies wiederholt werden, um veraltete Bauteile und Leiterbahnen zu löschen.

- KiCAD: Bauteile landen zunächst alle aufeinander, daher am Besten erst grob verteilen (lassen).

- EAGLE: Entfällt, denn die Platine übernimmt sofort die Änderungen des Schaltplans. Dafür geht die Platinendatei „kaputt“, wenn man nur die Schaltplandatei alleine geöffnet hat. (Wird normalerweise verhindert.)

# Bauteile platzieren: Grundregeln

Wegen **parasitärer Effekte**: „zusammengehörige Bauteile beieinander“

- Abblockkondensatoren nahe der Versorgungspins von ICs anbringen

- Isolationsabstand um Bereiche mit gefährlicher Spannung

- Empfindliche Empfänger oder Signalauswertungen entfernt von Leistungsteilen anbringen

- Für hohe Ströme: Wege kurz halten, große Leiterbahnbreite

Wegen **Fertigungstechnik**:

- Ausreichend Platz zwischen Bauteilen, um diese auch verlöten zu können

- Bauteile so anordnen, dass Leiterbahnen möglichst „entwirrt“ werden (Überkreuzungen benötigen Durchkontaktierung)

Und vieles mehr... siehe Literatur am Ende der Folien

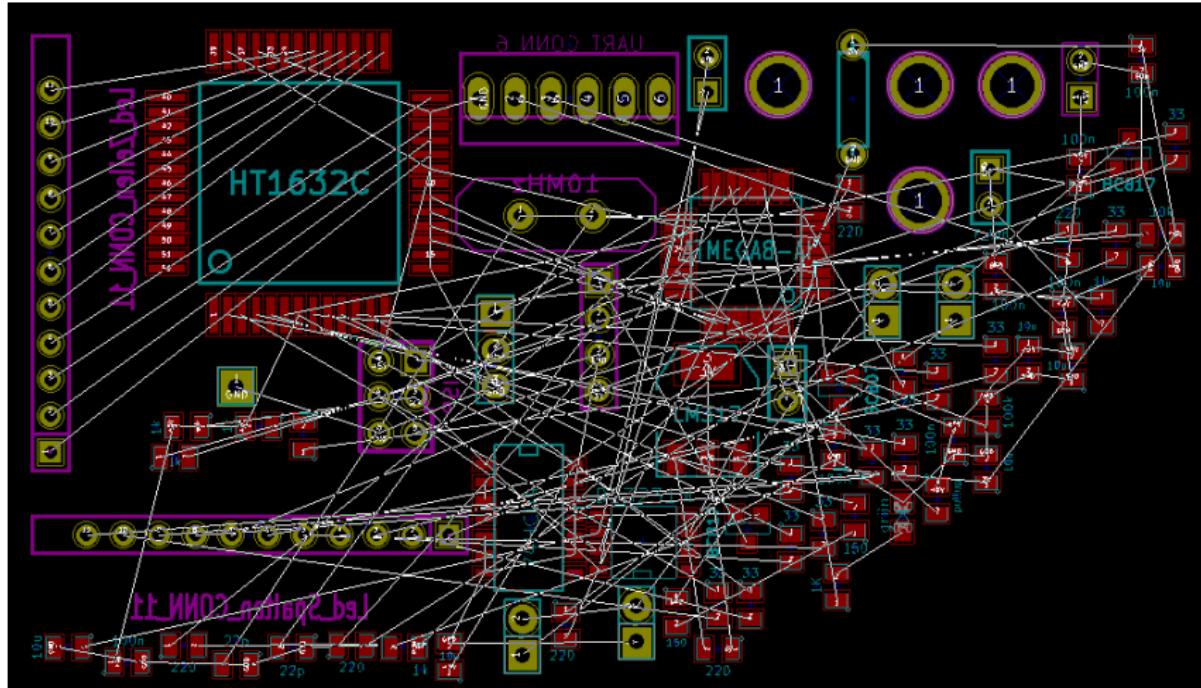

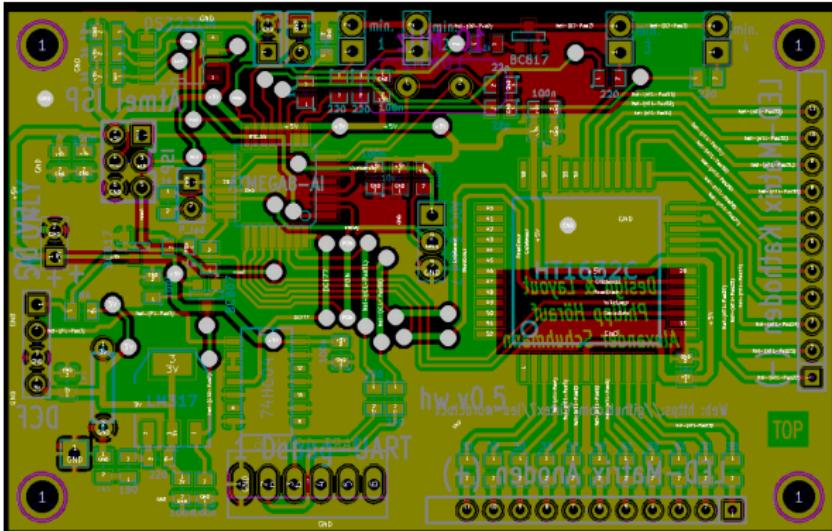

# Bauteile platzieren: „rat's nest“

„Rattennest“ zeigt Luftlinien zwischen zu verbindenden Pins.

Bauteile möglichst so anordnen, dass Luftlinien kurz und entwirrt sind.

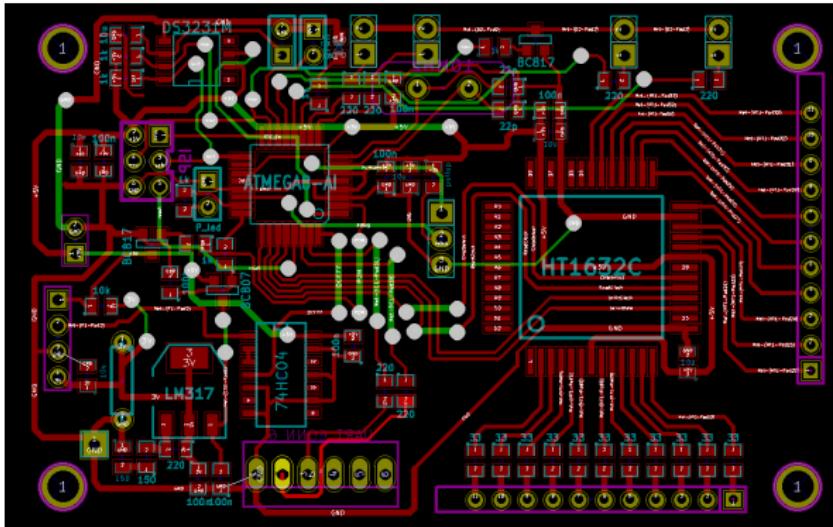

# Leiterbahnen legen (engl. *routing*)

- Leiterbahnen verbinden die Bauteile miteinander

- Wichtigstes zuerst verlegen (Versorgung, hoher Strom, schwache Signale)

- Für Überkreuzungen: Durchkontaktierungen (oder Drahtbrücken)

## Gute Praxis:

- Auf jede Kupferlage etwas Text

- Bezeichnung, Datum, Revision mit aufbringen

- ggf. Passermarken (u. a. bei Hobbyfertigung zweilagiger Platinen)

## Begründung:

- Fehler bei der Fertigung erkennen (gespiegelt? Lagen verrutscht?)

- Nachvollziehbarkeit (Welchen Stand hat diese Platine?)

## Gespiegelt oder nicht?

Am Bildschirm sieht man die Sicht von oben auf Bestückungsseite durch die Platine hindurch. Text auf der Lötseite (grün) muss gespiegelt aussehen, auf der Bestückungsseite (rot) nicht!

# Masseflächen

- Um Ätzchemie zu sparen und die Abschirmung und Leitfähigkeit zu verbessern, wird am Ende mit Massefläche aufgefüllt.

- Ausreichend Abstand einstellen, damit Pins lötbar bleiben

- Fläche sollte gut zusammenhängend sein (parasitärer Widerstand!)

# Design Rule Check (DRC)

Automatische, *nachträgliche* Prüfung des Layouts auf:

- Korrektheit (Kurzschlüsse, fehlende Verbindungen)

- Design-Regeln (zu kleine Abstände oder Leiterbahnbreiten)

## Fehlalarme?

Gibt es per Definition nicht, sofern Fertigungsgrenzen korrekt eingestellt!

Ausnahme: Bauteile mit so feinen Pin-Abständen, dass sie mit den gewählten Grenzen eigentlich nicht zu fertigen wären (aber man es trotzdem riskiert).

## Achtung: Selber mitdenken!

Dem DRC sollte nicht blind vertraut werden. Beispielsweise werden bei Hobbyfertigung Bauteil-Pins nicht durchkontakteiert, außer man verlötet sie beidseitig. Das Programm weiß das aber nicht!

# Unterstützung beim Leiterbahnen legen

**Online-DRC** (KiCAD, Altium, EAGLE ab V8.4): Programm verhindert DRC-Fehler bereits *während* die Leiterbahn verlegt wird:

„Verbogene“ Mausklicks werden ignoriert.

**Interaktives Routing** (bei KiCAD nur in OpenGL-Anzeige): Leiterbahn weicht Hindernissen aus oder schiebt andere Bahnen aus dem Weg (engl. *push-and-shove routing*). Benutzer gibt die Richtung vor.

**Automatisches Routing** (engl. *autoroute*) verlegt alles automatisch. Es ist mit großer Vorsicht zu genießen! Alles Wichtige unbedingt von Hand machen, oder bei Profi-Programmen wie Altium den Autorouter sehr genau konfigurieren. Für Hobby-Fertigung oder einlagige Platinen in der Regel nicht nutzbar, weil zu viele DuKos.

*Computers are good at following instructions,

but not at reading your mind. — Donald Knuth*

- Für Hobby-Fertigung: Ausdrucken (PDF, 1:1)

- für seitenrichtige Maske: Lötseite spiegeln

- für spiegelverkehrte Maske (FabLab): Bestückungsseite spiegeln

Vorteil: Druckertoner liegt direkt auf Platine

- Alternative zum Drucken: Photoplot machen lassen (Folie mit hohem Kontrast)

- Professionell: Gerber-Datenformat

- theoretisch: feste Norm

- praktisch: Hinweise des Fertigers genau beachten!

- Teilweise: Weitergabe im Originalformat (KiCAD/EAGLE/...)

- Gefahr von Fehlern durch Inkompatibilität verschiedener Versionen

- Gefahr von Datenklau: Quelldaten werden aus der Hand gegeben

42

## Platinenlayout: Allgemein

- A Practical Guide to High-Speed Printed-Circuit-Board Layout:

<http://www.analog.com/en/analog-dialogue/articles/high-speed-printed-circuit-board-layout.html>

- Linear Design Handbook, Chapter 12: Printed Circuit Board Issues

<http://www.analog.com/media/en/training-seminars/design-handbooks/Basic-Linear-Design/Chapter12.pdf>

- PCB Design Tutorial:

<http://alternatezone.com/electronics/files/PCBDesignTutorialRevA.pdf>

## Platinenlayout: KiCAD

- → siehe Übungsfolien

# Danksagung

---

Diese Präsentation basiert auf Vorarbeit von Philipp Hörauf.

Copyright: Philipp Hörauf und Max Gaukler, außer Bilder mit Quellenangabe.