| BP 2 Prozessorvergabe - Multiprozessoren: Aufgabenstellung                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <p><b>5 Prozessorvergabe in Multiprozessorsystemen</b></p> <p><b>5.1 Aufgabenstellung</b></p> <p><input type="checkbox"/> <b>Vom Betriebssystem zu unterstützende Ziele</b></p> <ul style="list-style-type: none"> <li>• Hoher Wirkungsgrad (performance)</li> <li>• Ausbaufähigkeit (scalability)</li> <li>• Hohe Verfügbarkeit (availability) und Zuverlässigkeit (reliability), sanfter Leistungsabfall bei Teilausfällen (graceful degradation)</li> </ul> | <p><input type="checkbox"/> <b>Spezielle Probleme, die aus dem Verlangen nach hohem Wirkungsgrad und Ausbaufähigkeit resultieren:</b></p> <ul style="list-style-type: none"> <li>• Zugriffsschutz in sehr großen Adressräumen (64 Bit für Adressen)</li> <li>• Vermeidung von Verklemmungen (deadlock prevention)</li> <li>• Ausnahmebehandlung bei sehr vielen Prozessoren</li> <li>• Effizient bearbeitbare Darstellung von asynchron arbeitenden oder bearbeitbaren Einheiten</li> <li>• Bereitstellung angepaßter Interaktionsmechanismen</li> <li>• Betriebsmittelverwaltung (Prozessorzuordnung, Speicherverwaltung)</li> <li>• Parallelisierung des Betriebssystems selbst</li> </ul> |

| 30.06.99<br>Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann<br>Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig                                                                                                                                                                                                                                | 5.1<br>30.06.99<br>Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann<br>Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BP 2 Prozessorvergabe - Multiprozessoren: Aufgabenstellung                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                 | <p><input type="checkbox"/> <b>Detaillierte Betrachtung der Prozessorvergabe</b></p> <ul style="list-style-type: none"> <li>• Unix-Prozeß bestehend aus Adressraum und Aktivitätsträger (heavyweight processes) <ul style="list-style-type: none"> <li>- Parallelisierung einer Aufgabe nur durch Benutzung mehrerer Prozesse; disjunkte Adressräume unnatürlich bei Datenpartitionierung</li> <li>- Erzeugung, Zuordnung und Tilgung von Prozessen aufwendig; dementsprechend zeitraubend ist der Wechsel zwischen seriellen und parallelen Phasen</li> <li>- Prozeßwechsel sind aufwendig wegen des damit verbundenen Kontextwechsels und den daraus resultierenden Cache- und TLB-Invalidierungen</li> </ul> </li> </ul> |

| 30.06.99<br>Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann<br>Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig | 5.2<br>30.06.99<br>Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann<br>Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BP 2 Prozessorvergabe - Multiprozessoren: Aufgabenstellung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <p><input type="checkbox"/> <b>Detaillierte Betrachtung der Prozessorvergabe</b></p> <ul style="list-style-type: none"> <li>• Unix-Prozeß bestehend aus Adressraum und Aktivitätsträger (heavyweight processes) <ul style="list-style-type: none"> <li>- Parallelisierung einer Aufgabe nur durch Benutzung mehrerer Prozesse; disjunkte Adressräume unnatürlich bei Datenpartitionierung</li> <li>- Erzeugung, Zuordnung und Tilgung von Prozessen aufwendig; dementsprechend zeitraubend ist der Wechsel zwischen seriellen und parallelen Phasen</li> <li>- Prozeßwechsel sind aufwendig wegen des damit verbundenen Kontextwechsels und den daraus resultierenden Cache- und TLB-Invalidierungen</li> </ul> </li> </ul> | <p><input type="checkbox"/> <b>Detaillierte Betrachtung der Prozessorvergabe (Forts.)</b></p> <ul style="list-style-type: none"> <li>• Entkopplung von Adressraum und Aktivitätsträger durch Kern-Fäden (middleweight processes, kernel-level processes, kernel-threads) <ul style="list-style-type: none"> <li>- Prozessorvergabe muß nicht mit Kontextwechsel verbunden sein; bei 'single task'-Betrieb keine Kontextwechsel</li> <li>- Bieten eine allgemeine Benutzerschnittstelle<br/>Beispiel: Mach, Windows NT</li> <li>- Betriebssystem macht Zuordnung und kann dabei seine Kenntnis des Systemzustandes nutzen, um gute Betriebsmittelauslastung zu erzielen</li> <li>- Für feingranulare Parallelität immer noch zu schwerfällig (z. B. ist bei manchen Rechensystemen Sicherung und Wiedereinsetzung der Register für Gleitkommabearbeitung aufwendig)</li> <li>- Verwaltungsoperationen für Fäden (z. B. im Rahmen von Interaktionen) erfordern Systemaufruf</li> <li>- Es ist unwahrscheinlich, daß eine (auch parametrierte) Zuordnungskonzeption für alle Anwendungen effizient ist.</li> </ul> </li> </ul> |

| 30.06.99<br>Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann<br>Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.3<br>30.06.99<br>Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann<br>Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BP 2 Prozessorvergabe - Multiprozessoren: Aufgabenstellung                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                 | <p><input type="checkbox"/> <b>Detaillierte Betrachtung der Prozessorvergabe</b></p> <ul style="list-style-type: none"> <li>• Unix-Prozeß bestehend aus Adressraum und Aktivitätsträger (heavyweight processes) <ul style="list-style-type: none"> <li>- Parallelisierung einer Aufgabe nur durch Benutzung mehrerer Prozesse; disjunkte Adressräume unnatürlich bei Datenpartitionierung</li> <li>- Erzeugung, Zuordnung und Tilgung von Prozessen aufwendig; dementsprechend zeitraubend ist der Wechsel zwischen seriellen und parallelen Phasen</li> <li>- Prozeßwechsel sind aufwendig wegen des damit verbundenen Kontextwechsels und den daraus resultierenden Cache- und TLB-Invalidierungen</li> </ul> </li> </ul> |

| 30.06.99<br>Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann<br>Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig | 5.4<br>30.06.99<br>Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann<br>Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BP 2 | Prozessorvergabe - Multiprozessoren: Aufgabenstellung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | <p>□ Detaillierte Betrachtung der Prozessorvergabe (Forts.)</p> <ul style="list-style-type: none"> <li>• Implementierung von leichtgewichtigen Fäden (lightweight processes, user level threads) durch Multiplexen schwer- oder mittelgewichtiger Fäden</li> <li>• Koordinierung <ul style="list-style-type: none"> <li>- Gegenseitiger Ausschluß</li> <li>- Bedingungsvariable</li> <li>- Leser/Schreiber-Koordinierung (optimiert für häufiges Lesen und seltenes Schreiben)</li> </ul> </li> <li>• Realisierung und Verwaltung durch Bibliotheken</li> </ul> |

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.5

| BP 2 | Prozessorvergabe - Multiprozessoren: Aufgabenstellung                                                                                                                                                                                                                                                                                                                                                       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | <p>□ Einfaches Beispiel</p> <pre>void mainline ( ... ) {     char int result;     thread_t helper;     int status      thr_create(0, 0, fetch, &amp;result, 0, &amp;helper);      // do something else for a while      thr_join(helper, 0, &amp;status);     // it's now safe to use result }  void fetch(int *result) {     // fetch value from a database      *result = value;     thr_exit(0); }</pre> |

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.7

| BP 2 | Prozessorvergabe - Multiprozessoren: Aufgabenstellung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | <p>◆ Beispiel: POSIX-Standard</p> <ul style="list-style-type: none"> <li>• Funktionalität <ul style="list-style-type: none"> <li>- Erzeugung von Fäden</li> <li>- Beendigung von Fäden</li> <li>- Verwaltung fadenspezifischer Daten</li> <li>- Signale zwischen Fäden</li> <li>- Identifikation von Fäden</li> <li>- Einplanung (Scheduling) von Fäden</li> <li>- Gegenseitiger Ausschluß zwischen Fäden</li> <li>- Bedingungsvariable (Monitore)</li> <li>- Leser/Schreiber-Koordinierung</li> <li>- Registrierung von Sonderbehandlungen bei fork()</li> </ul> </li> </ul> |

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.6

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.8

## Prozessorvergabe - Multiprozessoren: Aufgabenstellung

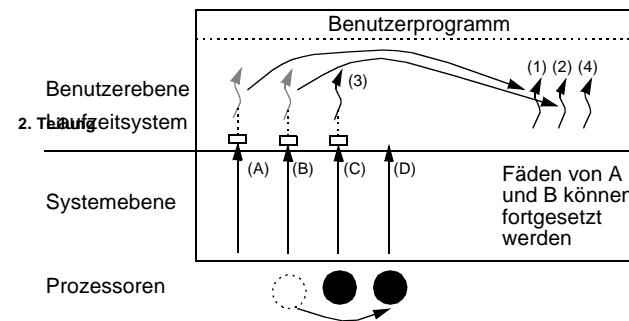

- **Einführung mehrstufiger (vor allem zweistufiger) Scheduler**

- Benachrichtigung des Schedulers der Benutzerebene über bestimmte Kernereignisse durch 'upcalls'

- Benachrichtigung des BS-Kerns über alle Ereignisse der Benutzerebene, die für das BS-Scheduling bedeutsam sind.

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.9

## Prozessorvergabe - Multiprozessoren: Kern-Fäden

- **Gemeinsame Bereitschlainge, aus der sich freie Prozessoren selbst bedienen:**

- Vorteil: Automatische Lastverteilung

- Nachteile: Keine Rücksichtnahme auf häufig interagierende Fäden

Keine Rücksichtnahme auf Reihenfolgeforderungen (z. B. beschrieben durch Präzedenzgraphen) und damit keine Gesamtoptimierung bezüglich der Aufträge (jobs)

- **Interaktionsorientiertes Scheduling (meist 'coscheduling' oder 'gang scheduling' genannt)**

Ousterhout entwickelte drei Methoden:

- Matrix-Scheduling (matrix)

- Fortlaufendes Scheduling (continuous)

- Ungeteiltes Scheduling (undivided)

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.11

## Prozessorvergabe - Multiprozessoren: Kern-Fäden

5.2

- ◆ **Prozessorvergabe für Kern-Fäden**

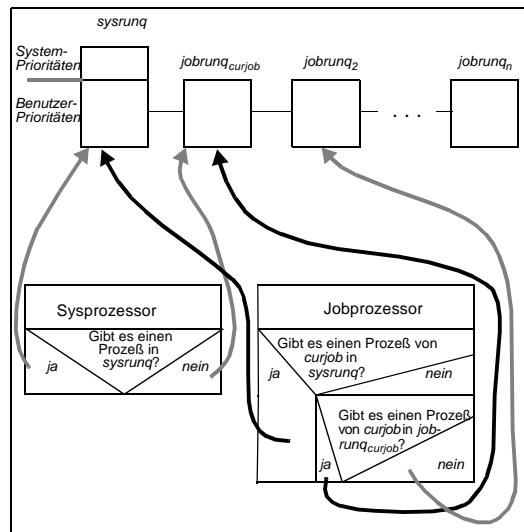

- ◆ **Scheduler-Struktur**

- Struktur der Warteschlangen

- Parallele Bearbeitung von Warteschlangen

- ◆ **Strategien**

- **Statische oder dynamische Zuordnung von Prozessor und Faden bei Mehrbenutzerbetrieb;**

### Ergebnisse der Untersuchungen von Zahorjan und McCann

(J. Zahorjan and C. McCann. Processor scheduling in shared memory multiprocessors. In *Proceedings of the 1990 ACM SIGMETRICS Conference on Measurement and Modeling of Computer systems*, pages 214-225, May 1990.):

- Unabhängig von der Einzel- und Gesamtlast ist dynamisches Scheduling am besten, wenn der Zusatzaufwand für Kontextumschaltungen gering ist.

- Die Vorteile dynamischer Zuordnung werden um so größer, je häufiger sich der 'Parallelitätsgrad' ändert.

- Die Vorteile dynamischer Zuordnung werden mit zunehmender Systemlast größer.

- Bezuglich der mittleren Antwortzeit ist dynamisches Zuordnen fast immer besser.

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.10

## Prozessorvergabe - Multiprozessoren: Kern-Fäden

◆

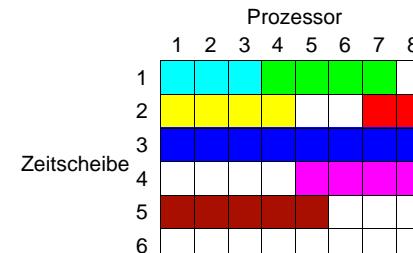

- ◆ **Matrix-Scheduling**

- Alle Fäden eines Auftrags in einer Zeile einordnen

- Fäden einer Zeile werden gleichzeitig zugeordnet

- Zeilen nach Round Robin zuordnen

- Löcher führen zu Effizienzverlusten

→ Jeder gemäß ausgewählter Zeile freie Prozessor sucht Faden in seiner Spalte

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.12

| BP 2 | Prozessorvergabe - Multiprozessoren: Kern-Fäden                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | <ul style="list-style-type: none"> <li>◆ <b>Fortlaufend</b> <ul style="list-style-type: none"> <li>- Matrix linearisiert durch Aneinanderreihung der Zeilen           <ul style="list-style-type: none"> <li>→ je <math>p</math> aufeinanderfolgende Zellen sind verschiedenen Prozessoren zugeordnet</li> </ul> </li> <li>- Zu jedem Zeitpunkt Fäden eines Fensters der Länge <math>p</math> zugeordnet</li> <li>- Neuankömmling wird in aktives Fenster aufgenommen, wenn dies möglich ist</li> <li>- Andernfalls wird Fenster solange nach rechts geschoben, bis zum erstenmal das linke Feld leer ist. Dies wird wiederholt, bis das Fenster genügend freie (nicht notwendigerweise aufeinanderfolgende) Zellen enthält. Dadurch Verringerung des Verschnitts!</li> <li>- Nach jedem Zeitquant wird Zuordnungsfenster weitergeschoben, bis der linke Eintrag zu einem Auftrag gehört, der im vorherigen Zeitschritt nicht vollständig zugeordnet war.</li> <li>- Nachteil: Unzusammenhängend gespeicherte Aufträge können beim Scheduling benachteiligt sein!</li> </ul> </li> </ul> |

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.13

| BP 2 | Prozessorvergabe - Multiprozessoren: Kern-Fäden                                                                                                                                                                                                                                                                                                          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | <ul style="list-style-type: none"> <li>◆ <b>Ungeteilt</b> <ul style="list-style-type: none"> <li>- Analog fortlaufend, aber nur zusammenhängende Einordnung</li> <li>- Der bei fortlaufender Einordnung erwähnte Nachteil verschwindet, dafür größerer Verschnitt</li> </ul> </li> <li>◆ <b>Es handelt sich um zentralisierte Algorithmen</b></li> </ul> |

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.14

| BP 2 | Prozessorvergabe - Multiprozessoren: Kern-Fäden                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | <ul style="list-style-type: none"> <li>◆ <b>Anderer Ansatz: baumartig angeordnete Controller verwalten Prozessoren ähnlich einem Buddy-Verfahren bei Speicherplatzvergabe.</b></li> <li>◆ <b>Präzedenzgraphorientierte Strategien</b> <ul style="list-style-type: none"> <li>• Die meisten Untersuchungen betreffen einstufige Präzedenzgraphen, d. h. ein Hauptfaden erzeugt eine Reihe von Unterfäden und beendet sich dann. Meist wird noch angenommen, daß die Unterfäden nicht interagieren.</li> <li>• <b>Bekannte Strategie für diesen Fall ist RR</b> <ul style="list-style-type: none"> <li>Erste Version führt Schlange von bereiten Fäden und bearbeitet sie nach RR, d. h. jeder freigewordene Prozessor bearbeitet den nächsten Auftrag für <math>Q</math> Zeiteinheiten und reiht ihn dann am Ende der Bereitschlange wieder ein.</li> <li>Zweite Version führt in der WS Aufträge. Falls ein Auftrag mehr Fäden besitzt als es Prozessoren gibt, wird innerhalb des Auftrags wiederum nach RR zugeteilt.</li> </ul> </li> <li>• <b>Probleme:</b> <ul style="list-style-type: none"> <li>Verdrängung während eines Spinlock oder in kritischem Abschnitt</li> <li>Häufige Kontextumschaltungen</li> </ul> </li> </ul> </li> </ul> |

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.15

| BP 2 | Prozessorvergabe - Multiprozessoren: Kern-Fäden                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | <ul style="list-style-type: none"> <li>• <b>Statische oder dynamische Partitionierung</b> <ul style="list-style-type: none"> <li>- Ziel ist die Minimierung der Kontextumschaltungen</li> <li>- Hypothese: Aufträge erreichen die beste Effizienz, wenn die Zahl der Fäden gleich der Zahl der verwendeten Prozessoren ist.</li> <li>- In NUMA-Architekturen existiert häufig eine von der Anwendung vorteilhaft nutzbare Kommunikationsstruktur; wegen ihrer guten Skalierbarkeit spielen Gitterarchitekturen eine besondere Rolle.</li> <li>- Als Strategien bieten sich Weiterentwicklungen der Matrixmethode von Ousterhout an.</li> </ul> </li> </ul> |

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.16

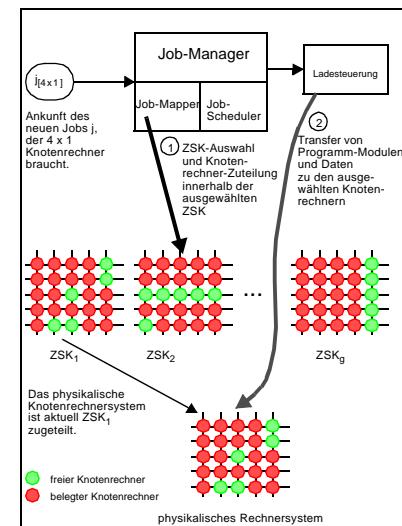

## BP 2 Prozessorvergabe - Multiprozessoren: Kern-Fäden

- Beispiel einer solchen Zuteilungsstrategie für ein torusartiges System, dessen Knoten Multiprozessoren sind (MEMSY):

### Definition

Eine **Zeitscheibenklasse (ZSK)** eines Parallelrechnersystems PS ist ein virtuelles Knotenrechnersystem, das folgende Eigenschaften hat:

- Die Anzahl der virtuellen Knotenrechner in ZSK ist gleich der Anzahl der physikalischen Knotenrechner in PS.

- ZSK hat die gleiche Verbindungstopologie wie PS.

- Es gibt eine bijektive Abbildung  $vps_{ZSK}$  der Knotenrechner von ZSK auf die Knotenrechner von PS. Gilt für ein  $V \in ZSK$  und ein  $R \in PS$   $R = vps_{ZSK}(V)$ , so sind V und R **topologisch äquivalent**. Dabei wird unter dem Begriff der **topologischen Äquivalenz** hier folgendes verstanden: Wenn den Systemen PS und ZSK jeweils das gleiche Koordinatensystem zugrundegelegt würde, dass die Knotenrechner bijektiv auf Koordinaten abbilden, so wären ein Knotenrechner  $K_v \in ZSK$  und ein Knotenrechner  $K_r \in PS$  topologisch äquivalent, wenn ihnen die gleichen Koordinaten zugeordnet wären.

## BP 2 Prozessorvergabe - Multiprozessoren: Kern-Fäden

- Knotenscheduling

## BP 2 Prozessorvergabe - Multiprozessoren: Kern-Fäden

- Einordnung neuer Aufträge

## BP 2 Prozessorvergabe - Multiprozessoren: Kern-Fäden

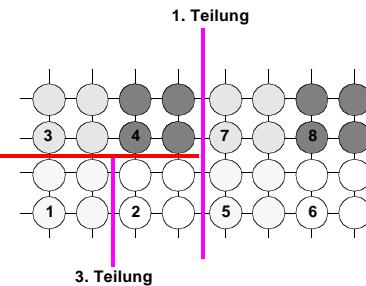

- Anpassung der eindimensionalen Buddy-Strategie

Ein Torus(8 x 4)-System, das aus Torus(2 x 2)-System-Einheiten basierend auf einer zweidimensionalen Buddy-Strategie aufgebaut wird.

Die Zahlen in den Knoten notieren die Reihenfolge, in der die entsprechenden (2 x 2)-Systeme hinzugefügt werden.

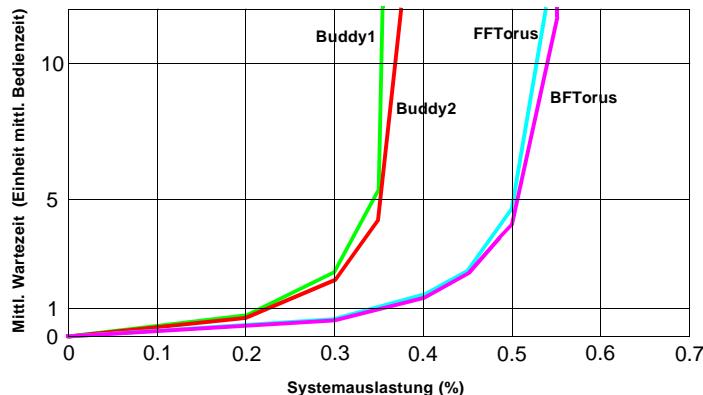

- ◆ Vergleich einiger ausgewählter Strategien mittels Simulation

- FFTorus: First-Fit angepaßt an Oberfläche eines Torus ohne Vorzugsrichtungen bei der Plazierung von Rechtecken

- BFTorus: Best-Fit angepaßt an Oberfläche eines Torus ohne Vorzugsrichtungen bei der Plazierung von Rechtecken

- Buddy1: Teilung gemäß Buddy-Strategie, vollständige Belegung eines 'Buddy'

- Buddy2: Teilung gemäß Buddy-Strategie, aber Belegung nur der wirklich benötigten Knoten

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.21

- ◆ Hand-off Scheduling

- Benutzer gibt Hinweise

- Hinweise auf Unzweckmäßigkeit des Zuordnens

- Hinweise auf zuzuordnende Prozesse

- Letzteres ist insbesondere im Zusammenhang mit Kooperation von Interesse.

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.23

#### Simulationsergebnisse für die vorangehenden Plazierungsstrategien

- exponentielle Verteilung der Zwischenankunftszeiten und Bedienzeiten

- Höhen und Längen der angeforderten Teilbereiche unabhängig gleichverteilt

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.22

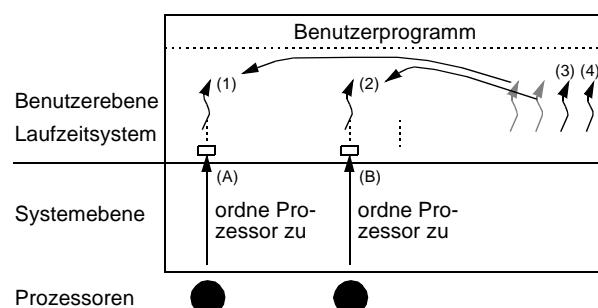

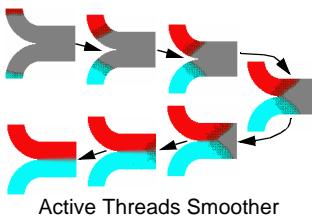

#### Mischung aus Kern- und Benutzerfäden

- Kern ordnet der Anwendung beispielsweise zwei Prozessoren zu

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.24

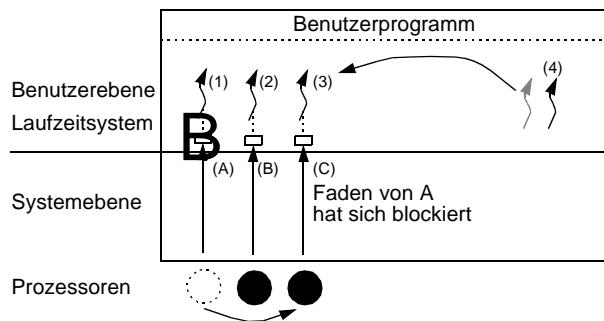

BP 2

## Prozessorvergabe - Multiprozessoren: Kern- und Benutzerfäden

- Ein Benutzerfaden blockiert sich im Kern wegen E/A

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg

ist ohne Genehmigung des Autors unzulässig

5.25

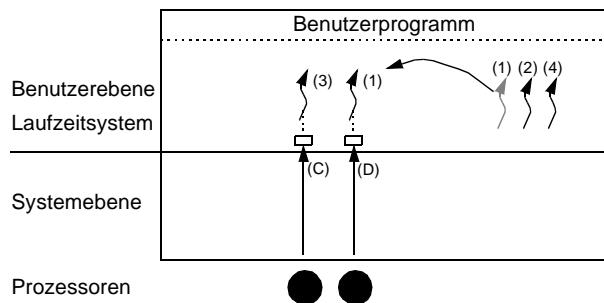

BP 2

## Prozessorvergabe - Multiprozessoren: Kern- und Benutzerfäden

- ‘upcall’ wegen freien Prozessors

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg

ist ohne Genehmigung des Autors unzulässig

5.27

BP 2

## Prozessorvergabe - Multiprozessoren: Kern- und Benutzerfäden

- E/A abgeschlossen

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg

ist ohne Genehmigung des Autors unzulässig

5.26

BP 2

## Prozessorvergabe - Multiprozessoren: Anwendungsfäden

### Prozessorvergabe auf Anwendungsebene (user level threads)

*Bellosa, F.: Three Dimensions of Scheduling. Arbeitsberichte des IMMD, Band 31, Nummer 12, Dezember 1998, 192 Seiten.*

Prozessorvergabe auf Anwendungsebene besser an Aufgabenstellung anpaßbar

- Alle Schedulingoperationen im gleichen Adressraum

- Reduktion von Fehlzugriffen

- Vergabealgorithmen können an Aufgabe angepaßt werden, z. B. Verzicht auf verdrängende Zuordnung

- Bessere Anpaßbarkeit der Datenstrukturen für Verwaltungsdaten

### Besondere Berücksichtigung der Fähigkeiten von NUMA-Architekturen möglich

- Möglichst keine globalen Datenstrukturen (Warteschlangen, Koordinierungsobjekte) wegen der Gefahr von Engpässen

- Zuordnung zu Prozessor mit gutem Zugang zu den benötigten Daten

- Vorausschauendes Puffern zur besseren Überlappung von Berechnung und Transport

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg

ist ohne Genehmigung des Autors unzulässig

5.28

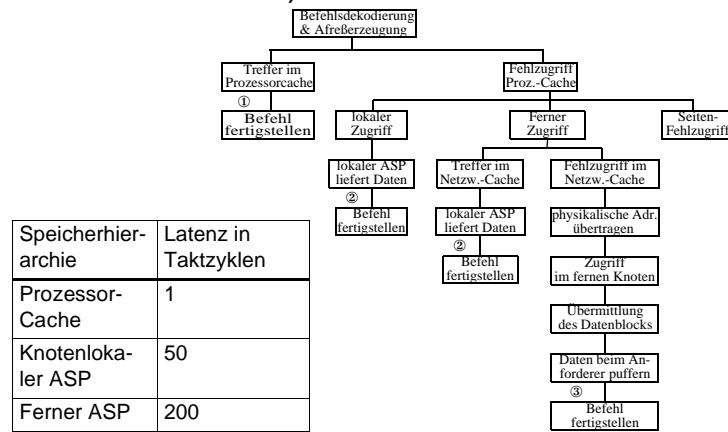

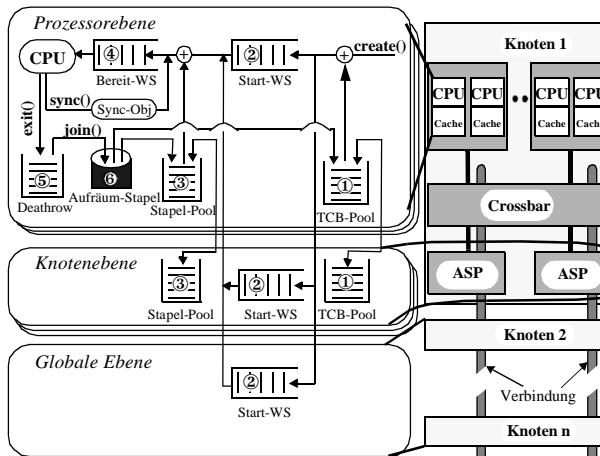

## BP 2 Prozessorvergabe - Multiprozessoren: Anwendungsfäden

- Beispielhafte Realisierung für Convex SPP 1000

(Architektur sehr ähnlich HP 9000 V2500):

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.29

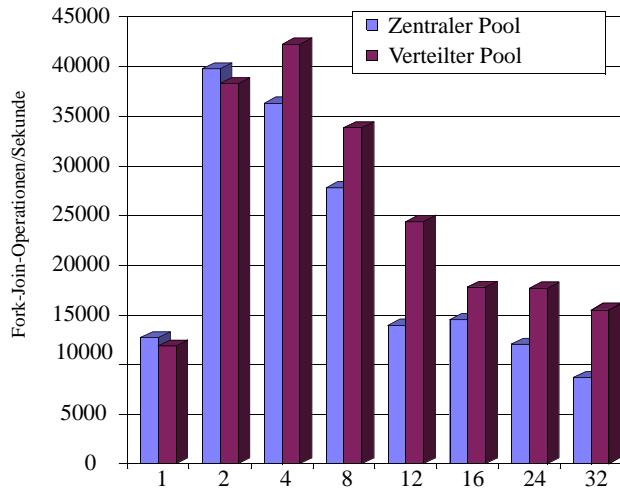

## BP 2 Prozessorvergabe - Multiprozessoren: Anwendungsfäden

- Vergleich zentraler und verteilter Haltung des Pools für Kontrollblöcke

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.31

## BP 2 Prozessorvergabe - Multiprozessoren: Anwendungsfäden

- Architektur der Datenstrukturen in Anlehnung an die Hardware-Architektur

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.30

## BP 2 Prozessorvergabe - Multiprozessoren: Anwendungsfäden

- Schnelle Umschaltung

- Durch Prozeßumwachalter-Fäden

- Vorausschauend

- Vergleich von Umschaltzeiten

| Operation                                                                    | Takt Zyklen |

|------------------------------------------------------------------------------|-------------|

| Kontextumschaltung zwischen Fäden mit den zugehörigen Informationen im Cache | 153         |

| Kontextumschaltung zwischen Fäden im gleichen Knoten                         | 1122        |

| Kontextumschaltung zwischen Fäden in unterschiedlichen Knoten                | 1805        |

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.32

## Prozessorvergabe - Multiprozessoren: Anwendungsfäden

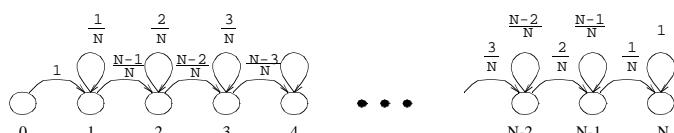

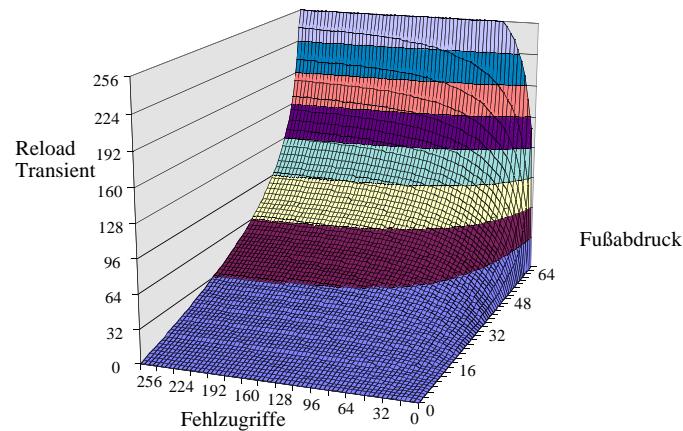

- **Reload Transient Model**

- ◆ Bei Zuordnung Berücksichtigung der Arbeitsmenge eines Fadens, die sich im Pufferspeicher befindet; im weiteren als "Fußabdruck" (footprint) bezeichnet

- ◆ Wie kann die Größe des Fußabdrucks ermittelt werden?

- ◆ Abschätzung anhand eines Markovmodells

- Laufende Fäden steigern die Zahl der gültigen Cachezeilen

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig 5.33

## Prozessorvergabe - Multiprozessoren: Anwendungsfäden

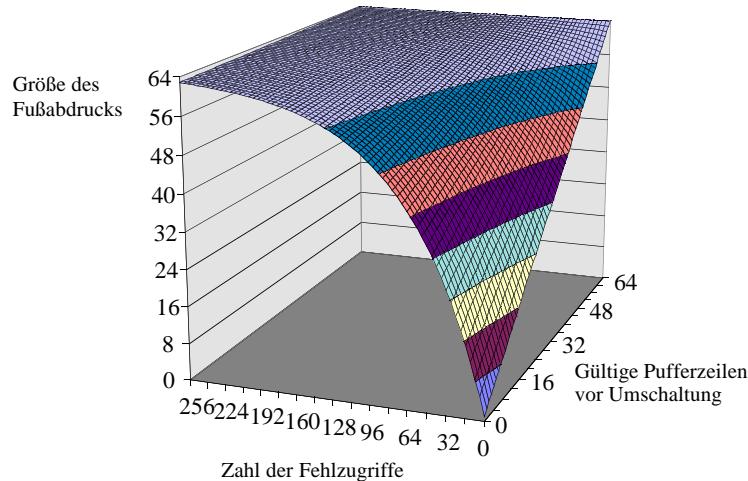

- Direkt abgebildeter Pufferspeicher, 64 Zeilen (ähnlich bei anderer Pufferzeilenzahl)

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig 5.35

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig 5.36

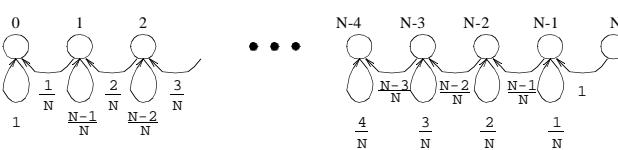

## Prozessorvergabe - Multiprozessoren: Anwendungsfäden

Zugehörige Übergangsmatrix

$$P = \begin{bmatrix} 0 & 1 & 0 & 0 & 0 & \dots & 0 \\ 0 & \frac{1}{N} & \frac{N-1}{N} & 0 & 0 & \dots & 0 \\ 0 & 0 & \frac{2}{N} & \frac{N-2}{N} & 0 & \dots & 0 \\ \vdots & & & & & \ddots & \vdots \\ 0 & & & & & 0 & \\ \dots & & & & & 0 & \frac{N-1}{N} & \frac{1}{N} \\ 0 & & & & & \dots & 0 & 1 \end{bmatrix}$$

→ Mittlere Größe  $E[F|V = v, M = n]$  des Fußabdrucks, wenn zunächst  $v$  Pufferzeilen gültig sind nach  $n$  Fehlzugriffen:  $F_v^n = \sum_{j=0}^N j \cdot P^n[v, j]$

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig 5.34

## Prozessorvergabe - Multiprozessoren: Anwendungsfäden

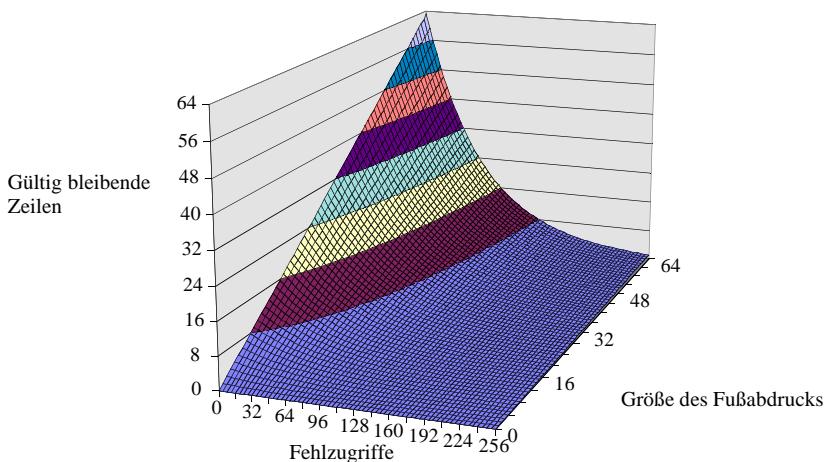

- ◆ Verlust gültiger Cachezeilen

- Blockierte Fäden verlieren Cachezeilen auf Grund von Fehlzugriffen anderer Fäden

30.06.99 Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig 5.36

BP 2

## Prozessorvergabe - Multiprozessoren: Anwendungsfäden

Mittlere Zahl  $E[V|F = f, M = n]$  gültig bleibender Zeilen, wenn zunächst v Pufferzeilen gültig sind, nach n Fehlzugriffen

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.37

BP 2

## Prozessorvergabe - Multiprozessoren: Anwendungsfäden

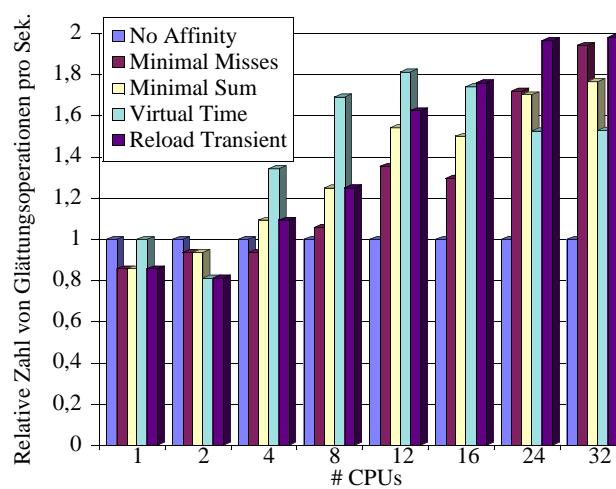

- ❑ **Messungen**

- ◆ **Verglichene Strategien**

1. *No Affinity*: Zuordnung nach LIFO

2. *Minimal Misses*: Zuordnung des jüngst zugeordneten

3. *Minimal Sum*: Zuordnung des Fadens, der während letzter Bearbeitung die wenigsten Fehlzugriffe verursachte

4. *Virtual Time*: Zuordnung des Fadens, der bislang die wenigsten Fehlzugriffe verursachte

5. *Reload Transient*: Zuordnung nach minimalem geschätztem Wiederherstellungsaufwand für seinen Fußabdruck

- ◆ **Beispiel:**

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.39

BP 2

BP 2

## Prozessorvergabe - Multiprozessoren: Anwendungsfäden

- Schätzung der erwarteten Fehlzugriffe beim Wiederanlauf

- Wiederanlauf des Threads mit minimalem Reload Transient

- Auswahl des Fadens mit dem geringsten Wiederherstellungsaufwand für seinen letzten Fußabdruck

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.38

BP 2

BP 2

## Prozessorvergabe - Multiprozessoren: Anwendungsfäden

30.06.99

Universität Erlangen-Nürnberg, IMMD IV, F. Hofmann

Reproduktion jeder Art oder Verwendung dieser Unterlage zu Lehrzwecken außerhalb der Universität Erlangen-Nürnberg ist ohne Genehmigung des Autors unzulässig

5.40