# **Betriebssysteme (BS)**

alias Betriebssystembau (BSB)

IA-32

das Programmiermodell der Intel Architektur

## Überblick

- Historie

- Basisprogrammiermodell

- Speicherverwaltung und Adressierung

- Schutz

- "Tasks"

- Zusammenfassung

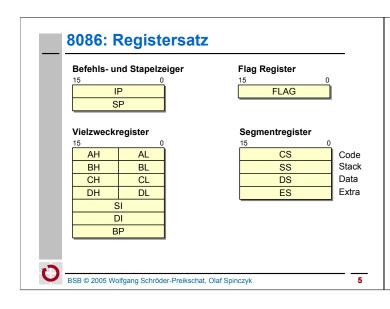

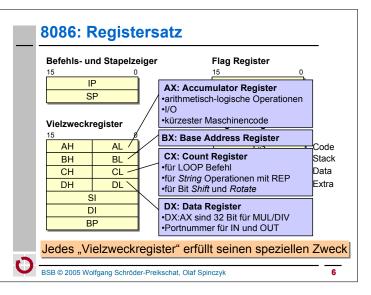

16 Bit Architektur

wenige Register

(jedenfalls aus heutiger Sicht)

kein orthogonaler Befehlssatz

- Real Mode. Virtual 8086 Mode

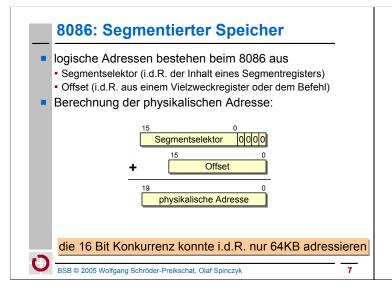

segmentierter Speicher

immernoch aktuell

Befehlslängen von 1 bis 4 Byte

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

8086: Programmiermodell

20 Bit Adressbus, d.h. maximal 1MB Hauptspeicher

#### Historie der Intel x86 Prozessoren

- **8086** (1978)

- der Urvater des PC Prozessors

- **80286** (1982)

- Einführung des Protected Mode

- segmentbasierter Speicherschutz

- erster IA32 Prozessor **80386** (1985)

- seitenbasierter virtueller Speicher

- integrierte FPU, RISC Ansätze **80486** (1989)

- **Pentium** (1993) - superskalar, 64 Bit Datenbus

- SMM, MMX, APIC, Dualprozessor-fähig

- **Pentium II** (1997) - Pentium Pro + MMX

- RISC-artige Mikroinstruktionen

- **Pentium III** (1999) - SSE

- Netburst Architektur Pentium 4 (2000)

- SSE2, Hyperthreading, Vanderpool, EM64T, Multicore

Aufwärtskompatibilität wird bei Intel groß geschrieben

obwohl von 1978 noch heute von jeder Pentium CPU unterstützt

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

#### 8086: Speichermodelle

- Programme können Adressen unterschiedlich bilden. Das Ergebnis waren unterschiedliche Speichermodelle:

- Tiny

- Code-, Daten- und Stacksegment sind identisch: 64K insgesamt

- Small

- Trennung des Codes von Daten und Stack: 64K + 64K

- Medium

- 32(20) Bit Zeiger f

ür Code, Daten- und Stapelseg. aber fest (64K)

- Compact

- Festes Code Segment (64K), 32(20) Bit Zeiger für Daten und Stack

- Large

- "far" Zeiger für alles: 1MB komplett nutzbar

- Huge

- wie "Large", aber mit normalisierten Zeigern

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

#### 8086: Fazit

- Urvater der PC Prozessoren

- bildete den Kern der ersten PCs

- noch heute sind Intel Prozessoren kompatibel

- Segmentregister brachten Vorteile

- trotz 16 Bit Architektur 1MB Speicher

- Trennung von logischen Modulen im Hauptspeicher

- Programm- und Übersetzerentwicklung ist aber vergleichsweise schwierig

- verschiedene Speichermodelle

- nicht orthogonaler Befehlssatz

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

10

#### IA-32 - die 32 Bit Intel Architektur

- die erste IA-32 CPU war der 80386

- 32 Bit Technologie: Register, Daten- und Adressbus

- heutige Systeme haben einen 64 Daten und 36 Bit Adressbus

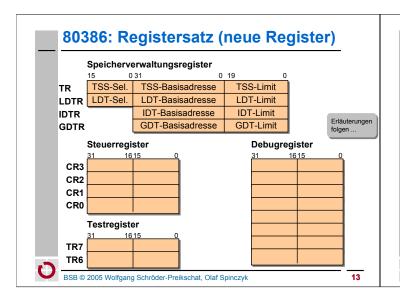

- zusätzliche Register

- komplexe Schutz- und Multitaskingunterstützung

- ursprünglich vom 80286 eingeführt

- Kompatibilität

- mit älteren Betriebssystemen durch den Real Mode

- mit älteren Anwendungen durch den Virtual 8086 Mode

- segmentbasiertes Programmiermodell

- seitenbasierte MMU

#### erweiterte Register heißen aus Kompatibilitätsgründen E... Befehls- und Stapelzeiger Flag Register EIP **EFLAG** FLAG **ESP** Vielzweckregister Segmentregister 1615 AH AL CS EAX Code ВН Stack BL SS **EBX** ECX СН CL DS Data EDX DH DL ES Extra ESI SI FS EDI DΙ GS EBP Erweiterung zum 8086

80386: Registersatz (Erweiterungen)

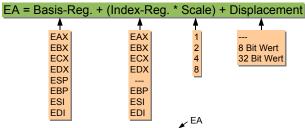

#### IA-32: Adressierungsarten

- Effektive Adressen (EA) werden nach einem einfachen Schema gebildet

- alle Vielzweckregister können dabei gleichwertig verwendet werden

- Beispiel: MOV EAX, Feld[ESI \* 4]

- Lesen aus Feld mit 4 Byte großen Elementen und ESI als Index

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

#### Das A20 Gate

- ... ist ein Relikt aus der Zeit der 80286 Systeme

- beim 8086 konnte es bei der Adressberechnung zu einem Überlauf kommen. Im Maximalfall:

- dies geschieht aus Kompatibilitätsgründen auch bei neueren PC Systemen

- um auch auf den Speicher oberhalb des ersten MB zugreifen zu können, muss das "A20 Gate" über ein Register des Tastaturcontrollers(!) umgeschaltet werden

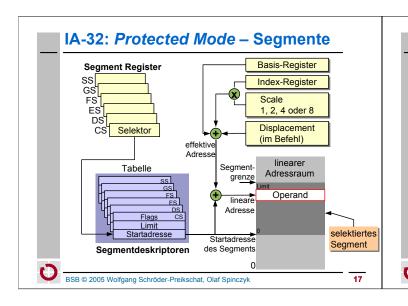

#### IA-32: Protected Mode – Segmente

- ein Programm (in Ausführung) besteht aus mehreren Speichersegmenten

- mindestens CODE, DATEN und STACK

- die Segmentselektoren beschreiben (indirekt) die Adresse und

- die "Lineare Adresse" ist Segmentstartadresse + EA

- Segmente dürfen sich im linearen Adressraum überlappen, z.B. dürfen die Segmentstartadressen bei 0 liegen. Dadurch wird ein "flacher" Adressraum nachgebildet.

- die "Lineare Adresse" entspricht der physikalischen Adresse, falls die Paging Unit (siehe entspr. Abschnitt) nicht eingeschaltet ist

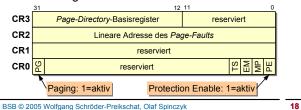

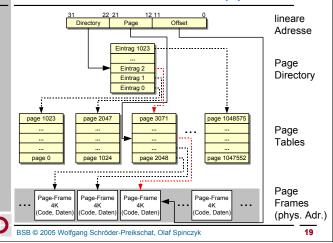

#### IA-32: Seitenbasierte MMU (1)

- Ein- und Auslagerung von Speicher (zwecks virtuellem Speicher) ist bei Segmentierung aufwändig. Daher bieten viele andere CPUs lediglich eine seitenbasierte Speicherverwaltung.

- ab dem 80386 kann eine **Paging Unit** (PU) optional hinzugeschaltet werden.

- die wichtigsten Verwaltungsinformationen stehen in den CRx Steuerregistern:

IA-32: Seitenbasierte MMU (2)

#### **IA-32: TLB**

- Problem: bei aktiver Paging Unit wäre eine IA-32 CPU erheblich langsamer, wenn bei jedem Speicherzugriff das Page Directory und die Page Table gelesen werden müssten

- Lösung: der *Translation Lookaside Buffer* (TLB):

- assoziativer Cache

- Tag: 20 Bit Wert aus Page Directory und Page Table Index

- Daten: Page Frame Adresse

- Größe beim 80386: 32 Einträge

- bei normalen Anwendungen erreicht der TLB eine Trefferrate von etwa 98%

- Schreiben in das CR3 Register invalidiert den TLB

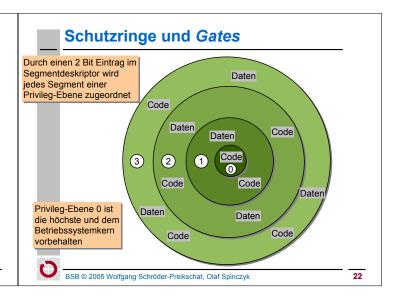

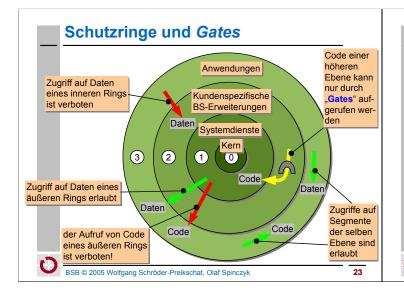

#### **Schutz**

- die wichtigste Eigenschaft des IA-32 Protected Mode ist das Schutzkonzept

- Ziel: fehlerhaften oder nicht vertrauenswürdigen Code isolieren

- Schutz vor Systemabstürzen

- Schutz vor unberechtigten Datenzugriffen

- keine unberechtigen Operationen, z.B. I/O Port Zugriffe

- Voraussetzungen: Code und Daten ...

- werden hinsichtlich der Vertrauenswürdigkeit kategorisiert

- bekommen einen Besitzer (siehe "Multitasking")

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

21

#### Segmentdeskriptoren weitere Informationen über die Schutzanforderungen der Segmente enthalten die Deskriptoren jede Verletzung führt zum Auslösen einer Ausnahme ein Segment-Deskriptor TYPE - Data: ED - Expansion Segment Base 31 ... 24 Limit 19 ... 16 +6 Direction W - Writable DPL TYPE Segment Base 23 ... 16 A - Accessed Segment Base 15 ... 0 TYPE - Code: C - Conforming Segment Limit 15 ... 0 - Readable - Accessed - Present Bit G - Granularity DPL - Descriptor Privilege Level D/B - 16/32 Bit Seq. - System Segment **AVL** - Available for OS BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk 24

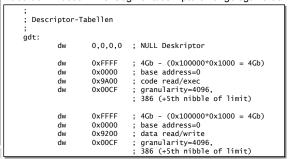

die meisten PC Betriebssysteme nutzen die Segmentierung nicht.

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

- 32 Bit Offset der logischen Adresse = lineare Adresse

- trotzdem müssen zwei Segmentdeskriptoren angelegt werden:

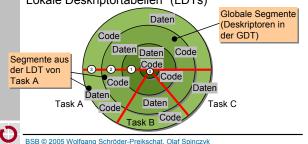

## Multitasking

- neben dem Schutz vor unberechtigten "vertikalen"

Zugriffen zwischen Segmenten unterschiedlicher Ebenen unterstützt IA-32 auch ein Task-Konzept ("horizontale Trennung)

- die Zuordung von Segmenten zu Tasks erfolgt über "Lokale Deskriptortabellen" (LDTs)

# Lokale Segmentdeskriptortabellen

... sind nötig, wenn der Segmentselektor (z.B. aus einem Segmentregister) sich auf die LDT bezieht:

| 15    | 3 2 1 0  |             |

|-------|----------|-------------|

| Index | TI RPL   | TI = 0: GDT |

|       | <b>*</b> | 11 - 1. LD1 |

... werden mit Hilfe des LDTR gefunden, das bei jedem Taskwechsel ausgetauscht wird:

#### Speicherverwaltungsregister

|      | 15 0     | 31 0             | 19        | 0 |

|------|----------|------------------|-----------|---|

| TR   | TSS-Sel. | TSS-Basisadresse | TSS-Limit |   |

| LDTR | LDT-Sel. | LDT-Basisadresse | LDT-Limit |   |

| IDTR |          | IDT-Basisadresse | IDT-Limit |   |

| GDTR |          | GDT-Basisadresse | GDT-Limit |   |

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

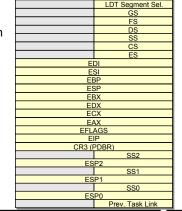

#### Der Task-Zustand: TSS Segmente

- das Task Register TR verweist auf eine Daten-struktur, die den kompletten Task-Zustand aufnimmt

- bei einem Task-Wechsel (siehe nächste Seite) wird der komplette Zustand gesichert und der Zustand des Ziel-Tasks geladen

- alles in Hardware!

26

25

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

#### Task-Wechsel

- für einen Task-Wechsel benötigt man entweder ...

- ein Task-Gate in der GDT, einer LDT oder der IDT (Task-Wechsel bei Unterbrechungen!)

- oder einfach nur einen TSS Deskriptor in der GDT

- ausgelöst werden kann ein Wechsel durch ...

- eine JMP Instruktion

- eine CALL Instruktion

- eine Unterbrechung

- eine IRET Instruktion

- Nested Tasks: bei Unterbrechungen und CALLs wird das NT Flag im EFLAGS Register und der "Prev. Task Link" im TSS gesetzt. Wenn dies der Fall ist, springt IRET zum vorherigen Task zurück.

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

29

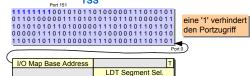

## **Ein-/Ausgaben im Protected Mode**

- nicht jeder beliebige Task darf Ein-/Ausgabe durchführen!

- Zugriffe auf Geräte im Speicher (memory-mapped I/O) können über Speicherschutz abgefangen werden

- Zugriffe auf I/O Ports werden eingeschränkt:

- die I/O Privilege Level Bits im EFLAGS Register erlauben Ein- und Ausgaben auf bestimmten Schutzringen

- auf den anderen Ebenen regelt die I/O Permission Bitmap f

ür jeden Task und Port der Zugriff:

den Abschluss bildet immer ein Byte mit 0xff

BSB © 2005 Wolfgang Schröder-Preikschat, Olaf Spinczyk

30

## IA-32: Was gibt es sonst noch?

- Physical Address Extension (PAE)

- moderne Pentium CPUs haben 36 Bit physikalische Adressen

- erweiterte Page Table Einträge

- weitere Page Directory Ebene

- System Management Mode (SMM)

- gibt dem BIOS Kontrolle über das System

- das Betriebssystem merkt davon nichts!

- Virtualisierung der CPU

- der Virtual 8086 Mode

- 16 Bit Anwendungen oder Betriebssysteme laufen als IA-32 Task in einer geschützten Umgebung

- ganz neu: "Vanderpool Technology"

- Hardwareunterstützung für virtuelle Maschinenlösungen wie VmWare, VirtualPC oder Xen

- erlaubt die Ausführung von Ebene 0 Protected Mode Code in einer VM

#### Zusammenfassung

- die IA-32 Architektur ist ausgesprochen komplex

- segmentbasierter und seitenbasierter Speicherschutz

- Hardwareunterstützung für Multitasking

- Task-Aktivierung bei Unterbrechungen

- Schutz von I/O Ports pro Task

- ...

- viele dieser Features werden von heutigen Betriebssysteme nicht genutzt

- typisch ist der flache Adressraum mit aktiver Paging Unit

- "schwergewichtige Prozesse" sind nicht für jede Anwendung nötig

- bemerkenswert ist auch die konsequente Kompatibilität mit älteren Prozessorversionen

- Stichwort "PIC" und "A20 Gate"!