# Design and Implementation of a Transparent Memory Encryption and Transformation System

Diplomarbeit aus der Informatik

vorgelegt von

Alexander Würstlein

begonnen am 1.4.2012

fertiggestellt am *26.8.2012*

angefertigt am

Lehrstuhl für Informatik 4 (Verteilte Systeme und Betriebssysteme) Friedrich-Alexander-Universität Erlangen-Nürnberg

betreut von

Wolfgang Schröder-Preikschat Michael Gernoth

## Erklärung

Hiermit erkläre ich gemäss der Diplomprüfungsordnung, «dass die Arbeit ohne fremde Hilfe und ohne Benutzung anderer als der angegebenen Quellen angefertigt wurde und dass die Arbeit in gleicher oder ähnlicher Form noch keiner anderen Prüfungsbehörde vorgelegt und von dieser als Teil einer Prüfungsleistung angenommen wurde. Des weiteren [...], dass alle Ausführungen, die wörtlich oder sinngemäß übernommen wurden, als solche gekennzeichnet sind. »

Erlangen, den 26.8.2012

Alexander Würstlein

## **Abstract**

Starting from the hardware-based mitigation of cold-boot attacks by transparently encrypting portions of RAM, a novel approach to supplement computer systems through the application of transparent transformations on memory areas is presented. This work provides a working, proof-of-concept implementation of such a system on an FPGA-based PCI Express card. More general possible transformations and applications such as data integrity and consistency, aggregation and processing or transactional memory are discussed.

## Kurzzusammenfassung

Inspiriert von der Idee der hardware-basierten Vorbeugung sogenannter «Cold-Boot»-Angriffe durch transparente Verschlüsselung von Teilen des Arbeitsspeichers wird ein neuartiger Ansatz vorgestellt, um die Funktionalität von Rechnersystemen durch die Anwendung transparenter Transformationen auf Speicherbereiche zu erweitern. Diese Arbeit präsentiert einen funktionsfähigen Prototypen eines solchen Systems basierend auf einer über PCI Express angebundenen FPGA-Karte. Mögliche Transformationen und Anwendungen wie beispielsweise Datenintegrität und -konsistenz, Datensammlung und -verarbeitung oder «transactional memory» werden erläutert.

# Contents

| 1 | I   | ntroduction                                                        | 7  |

|---|-----|--------------------------------------------------------------------|----|

|   | 1.1 | Motivation                                                         | 7  |

|   | 1.2 | Scope of this Work                                                 | 8  |

|   | 1.3 | Related Work                                                       | 10 |

| 2 | P   | PCI Express                                                        | 11 |

|   | 2.1 | Topology and Lower Protocol Layers                                 | 12 |

|   | 2.2 | Data Link Layer Protocol                                           | 13 |

|   | 2.3 | Transaction Layer Protocol                                         | 13 |

|   | 2.4 | DMA and Device Memory                                              | 18 |

| 3 | F   | PGAs                                                               | 23 |

|   | 3.1 | FPGAs as Programmable Hardware                                     | 23 |

|   | 3.2 | Hardware Description Languages                                     | 24 |

|   | 3.3 | Toolchain                                                          | 28 |

|   | 3.4 | IP Cores                                                           | 29 |

|   | 3.5 | The Wishbone Bus                                                   | 31 |

| 4 | I   | mplementation                                                      | 33 |

|   | 4.1 | PCI Express FPGA Card                                              | 33 |

|   | 4.2 | Xilinx PCI Express Endpoint Core                                   | 34 |

|   | 4.3 | First Tests with the Example Application                           | 34 |

|   | 4.4 | Bespoke Implementation of TLP Generation and Application Interface | 36 |

|   | 4.5 | XOR Application                                                    | 47 |

|   | 4.6 | AES Application                                                    | 47 |

|   | 4.7 | Linux Kernel Module and Test Programs                              | 50 |

6 Contents

| 5 | P   | Results and Measurements   |

|---|-----|----------------------------|

|   | 5.1 | Proof of Concept           |

|   | 5.2 | Benchmarks                 |

| 6 | F   | future Work and Conclusion |

|   | 6.1 | Future Improvements        |

|   | 6.2 | Applications               |

|   | 6.3 | Conclusion                 |

## Chapter 1

## Introduction

### 1.1 Motivation

To allow for further development of computer systems and their operating systems, a continued exchange of concepts and ideas between software developers creating new operating systems and hardware developers creating new hardware concepts is necessary. However, very often, this exchange is hindered by the necessarily more abstract nature of the discussions: The implementation of new hardware features is a time-consuming and resource-intensive task compared to the development of software. It is not only necessary for communication between the diverse groups of hardware and software developers to take place, but also the hardware feature in question needs to be implemented to test it and judge its fitness and viability for its intended purpose, which is usually very expensive. Therefore promising ideas will often be discarded prematurely because of lacking expertise and resources for hardware development.

This situation could, at least in part and for some types of hardware, be alleviated by using programmable hardware in the form of «Field Programmable Gate Arrays (FPGAs)». FPGAs are available in various forms and sizes, but generally within the reach of all but the smallest budgets. Necessitated by the faster development cycles today and the sinking costs of FPGAs, they even appear in larger numbers in some consumer devices. One example of such a consumer device is the popular «FritzBox» router appliance[1, 2]. Therefore the assumption seems warranted, that through FPGAs, the introduction of new hardware features to support operating systems and applications might be easier.

Yet the amount of work happening in this direction seems relatively low. This is likely due to two factors: First, the still relatively complicated process of developing hardware. Hardware development happens on a very low level of abstraction and can be very tedious because of the relatively long cycles of coding, compiling and testing, lacking tools and the opaque nature of hardware. Second, as there is no large body of previous work, the potential of hardware development seems hardly known.

Thus, the first motivation of this work is to improve on this situation by providing a flexible, high-level abstraction that can be used as a model to demonstrate various possible features that software developers have always wanted, but which hardware has never provided.

The second motivation comes from a problem that is hardware-related in nature, but where all current attempts at a solution are essentially software-based. Cold-boot attacks on data and encryption keys in the RAM of a computer system make use of the fact that RAM holds its contents for a few minutes when sufficiently cooled. This makes it possible to physically extract the RAM modules, plug them into another computer and copy the contained data or encryption keys.

Software-based mitigations for these attacks like «TRESOR»[3] or others[4] hide encryption keys or delete them when an unusual condition is detected or during normal operation, incurring a, sometimes severe, performance penalty. Such mechanisms can be made transparent to application software and even to the operating system via a hypervisor[5]. When looking at the quite elaborate tricks like hiding keys in the processor's debug registers or cache, the question rises: why is normal hardware unable to provide transparent memory encryption and facilities to store the key in use.

If the encryption and decryption were to happen transparently in specialised hardware, the problem —that key extraction is simply the physical extraction of a memory module— would be turned into the hopefully much harder problem of extracting the key from a register of an uncooperating FPGA, that does not just allow an attacker to read register contents. The transparency of the encryption and decryption operation would also simplify the implementation on the operating system side and could improve performance of the whole setup.

## 1.2 Scope of this Work

Considering both of these motivations, I intend to create an abstraction layer or module that is capable of transparently encrypting and decrypting portions of memory. The module or abstraction layer should be hardware-based and therefore transparent even to the operating system, with the reasonable restriction that of course some initalisation and configuration of the hardware might be necessary.

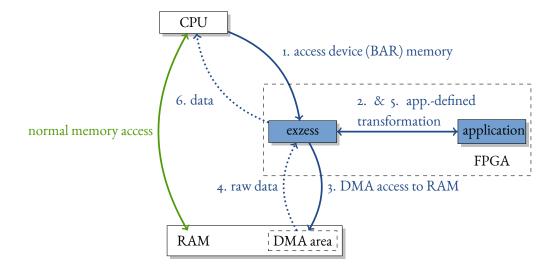

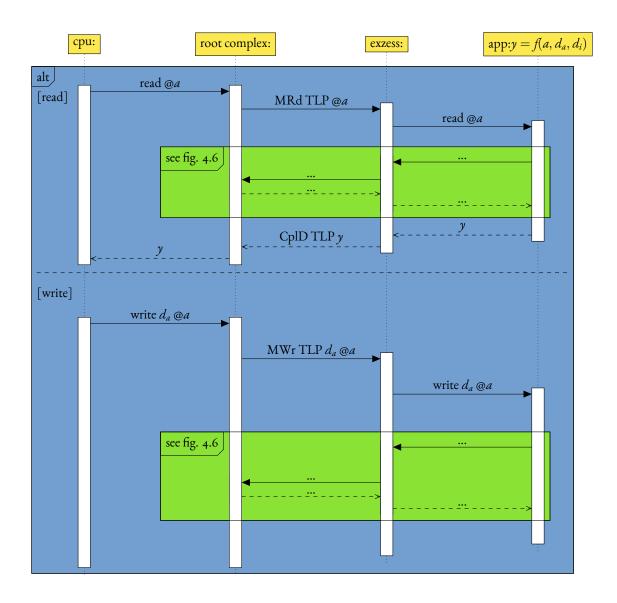

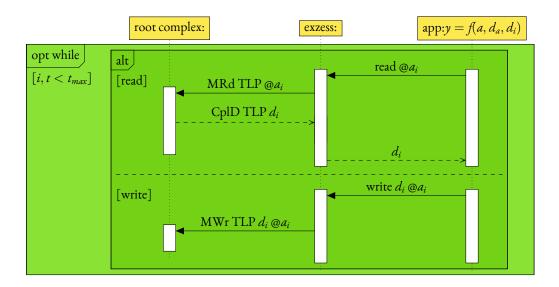

The module should also be capable of more generally supporting arbitrary hardware-defined mappings of memory, where encryption and decryption is just one possible mapping. Others should be definable by exchanging the mapping application. This might enable applications such as consistency checks on the stored data, error correction, transactional semantics or advanced access controls on memory areas. A schematic overview of the transformation process is shown in figure 1.1.

As a hardware platform, an FPGA on a PCI Express card, namely a «Xilinx Spartan-6» on an «Enterpoint RaggedStone2» development board will be used. PCI Express seems the logical choice given its perfomance and ubiquity as well as the future prospect of technologies like Thunderbolt being based on PCI Express. The Xilinx Spartan-6 FPGA is a viable choice because the necessary physical interface for PCI Express as well as a freely usable IP core for the PCI Express interface are available.

Figure 1.1: Schematic view of the «exzess» abstraction and application to be implemented. Shown is a reading or writing memory access to a memory area assigned to the FPGA device from the CPU (step 1). The exzess module communicates with the application (step 2), which transforms the original request by transforming the request address and/or request data. The exzess module will execute this transformed request on its assigned DMA area (step 3). Optionally, on a reading access, the raw data read from the DMA area will be returned to the exzess module (step 4), which will again let the application perform its transformation (step 5). The read data will then be returned to the CPU (step 6). Normal memory accesses (green) to addresses not belonging to the device memory area (or BAR area) of the FPGA will not be affected.

The RaggedStone2 card is a platform providing the aforementioned FPGA and PCI Express interface with the necessary development infrastructure like JTAG interface and flash memory.

This diploma thesis will first introduce the reader to the important technologies that are necessary to understand the implementation. First the various layers of the PCI Express protocol and important aspects of memory access in PCI Express systems will be discussed, followed by an introduction to FPGAs and hardware development on and using FPGAs. After an introduction of the relevant IP cores and the Wishbone on-chip bus system, the implementation will be explained in detail. Starting from the hardware the implementation will run on, the FPGA abstraction called «exzess» will be introduced as well as implemented example applications which make use of the «exzess» abstraction. The operating system interface and userspace infrastracture to access, test and benchmark the FPGA will also be described. The work will end with a discussion of possible further applications besides those implemented and already described as well as an evaluation of the implemented applications' performance and viability, finally completed by an outlook and conclusion.

## 1.3 Related Work

Related work exists regarding various aspects of this work, but no similar combination of these various aspects is known to me. Therefore I will discuss the related work separately for each aspect.

As mentioned before in section 1.1, there is a large body of work towards software-based mitigation of cold-boot attacks[3, 5, 4]. Usual lines of work in this area aim to hide the key material in cache[4] or CPU registers[3, 5].

Other mitigation strategies[6] suggest the use of hard-disk drives with built-in encryption functions. In some limited scenarios, where the added expense of replacing hard-disks is warranted and where problems like multi-user-access do not exist, such self-encrypting hardware is an option. Yet this would only solve the cold-boot problem in the context of whole-disk-encryption, the danger to other kinds of key material like signing keys through the same attack can not be mitigated by this.

Similarly, CPU register based approaches like TRESOR[3] are limited to very small amounts of key material. Others that hide keys in cache[4] fare better in this regard, as cache sizes range from kilobytes to megabytes. However, excessive performance penalties prevent the use of cache-based techniques at normal system run-time, therefore the keys are usually only moved into the cache when a suspend or sleep mode is initiated.

The hardware-based encryption method presented in this work provides improvements over the mentioned approaches. First, no performance penalty for the system is incurred except when accessing the key material, and this penalty could be lessened by the use of caching (which this work does not implement). The amount of storable material in the encrypted area is only limited by the available amount of RAM and address space. In extreme cases, some variant of «almost-whole-RAM» encryption might be viable. Furthermore, because the encryption is transparent to both applications and the operating system, except for a device driver for initialisation and assignment of the encrypted memory resources, virtually any kind of cryptographic key material or important data is protectable.

On the subject of providing memory mapping transformations as described in the introduction, the literature is even less yielding. While the use of DMA is certainly widespread in the industry [7, 8, 9] (e.g. to accelerate computations of various kinds and provide easy and fast data access to the accelerating FPGA) and access to device memory or device register space is even more widespread, no combination of the kind described in this work could be found.

Similarly, as described in the same publications[8, 9], the use of FPGAs as coprocessors for mostly number-crunching applications is well-known. To the best of my knowledge, no work has been published on the use of FPGAs as coprocessors in other contexts like the one described in this work.

Consequently, this work provides a novel approach —transparent memory transformations—that enables various new applications.

## Chapter 2

## PCI Express

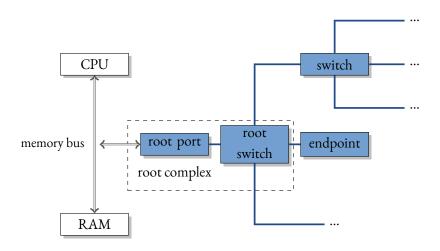

Figure 2.1: Architecture of a PCI Express system

Modern personal computer systems generally use «PCI Express»[10, 11] as bus system to connect onboard and extension-card-type peripherals. The PCI Express bus system was specified in the «PCI Express Base Specification»[10]¹. PCI Express was developed to replace the older «Peripheral Connect Interface (PCI)» family of busses and protocols. While the earlier technologies «PCI», «PCI-X» and «PCI-64» were parallel busses with a shared, arbitrated medium, PCI *Express* changed this to a tree topology with serial point-to-point links between the nodes of the tree.

Some of the terminology that comes with PCI Express is somewhat unusual, both in the context of communication protocols and bus systems. For example, what is called a «Transaction Layer Packet (TLP)» in PCI Express terminology would be called «frame» in Ethernet and other network systems.

<sup>&</sup>lt;sup>1</sup>At the time of writing the PCI Express base specification was available in revision 3.0.

To be consistent with existing documentation on PCI Express and hardware used for this work, the PCI Express terminology will be used.

This work and the following discussion will be based on the 1.0 and 1.1 revisions of the PCI Express Base Specification[10], since available hardware and IP cores are based on revision 1.1 and available literature are similarly limited. Obtaining the specification is also very costly. The PCI Express Base Specification will usually be referred to as the «specification» within this chapter.

## 2.1 Topology and Lower Protocol Layers

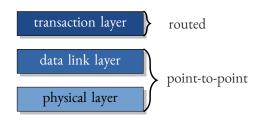

Figure 2.2: PCI Express protocol layers

## 2.1.1 Structure of a PCI Express system

PCI Express forms a switched, hierarchical, tree-shaped network. Inner leaves of this tree are called «switches», outer nodes are called «endpoint devices», corresponding to the respective functions inside the network. Examples of endpoint devices are plug-in cards, such as a network interface card, or soldered-on chips on the mainboard like an integrated graphics processor. Each switch has at least one «upstream» port and one or more «downstream» ports. These directions denote whether a port is a link to a higher or lower level within the tree hierarchy. The root node, called «root complex», is formed by the PCI Express «root switch» and «root port». The root switch and port are usually combined in one device as part of the mainboard chipset of a computer system.

The root port has the special role of being the interface between the PCI Express bus, the CPU and the main memory of the computer system. During the boot process when the connected peripherals of the computer system are discovered, the PCI Express root port is used as starting point for the subsequent discovery of deeper levels of the switch and device hierarchy. Configuration requests and other «housekeeping tasks» are performed through the root port.

Accesses to main memory —called «Direct Memory Access (DMA)»— from PCI Express devices are processed by the root port. In the other direction, accesses from the CPU to device memory are also issued via the root port. In both cases, the root port acts as a gateway between the CPU and RAM on one side and the PCI Express devices on the other side.

### 2.1.2 Physical Layer

The physical layer of PCI Express was designed with the primary requirements of speed and flexibility in mind. Many older bus systems like the predecessor to PCI Express, PCI, were based on parallel links. In a parallel bus, there is a larger number —e.g. 32 for PCI— of signal lines carrying data. For error-free transmission of data it is essential that on all data lines, all bits that belong to one data word arrive within the same clock cycle of the bus clock.

If the length s of those data lines differs by more than  $\Delta s \gtrsim \tau \cdot v_g$  where  $\tau$  is the length of a clock cycle and  $v_g$  is the speed of signal propagation, this condition is violated. While for a clock frequency of 100 MHz allowable values for  $\Delta s$  are of the order 3 mm to 6 mm. For 1 GHz or higher,  $\Delta s$  needs to be 1 mm or lower. Because these constraints are hard to meet when designing circuit boards, a reduction in the number of signal lines is necessary with higher speeds.

Therefore, like many current bus and communication technologies such as SAS/SATA or USB, PCI Express uses serial data paths. A PCI Express «port» or «link» may consist of one or more «lanes» (up to 32) with independent clocks. This allows high clock frequencies in combination with increased capacity by using multiple parallel data pathways if neccessary. The number of lanes in a port or link is given in a notation prefixed with  $\ll x \gg$ , so  $\ll x16 \gg$  means that a port or link has 16 lanes and therefore 16 times the theoretical capacity of a  $\ll x1 \gg$  link or port.

The relation between ports and links is simply that each device has a number of ports with a given maximum number of lanes. When connecting two ports, a link is formed by negotiating connection parameters like available lanes, etc.

Each lane consists of two data transmission lines, using differential signaling. Data is encoded using the «8b10b» encoding, which allows for the clock signal to be generated from the data lines. Additional symbols in the 8b10b encoding, which are not needed for data transmission are used as start and end symbols for transaction layer and data link layer packets as well as for link training and transmission error signalling.

## 2.2 Data Link Layer Protocol

The «data link layer protocol (DLLP)» defines the communication between the two sides of a single PCI Express link, e.g. an endpoint and the switch it is connected to. The DLLP is responsible for acknowledging the receipt of certain TLPs, flow control, link error checking and power management functions.

## 2.3 Transaction Layer Protocol

An important part of this work consists of implementing the handling of TLPs, therefore the following discussion of the transaction layer will be more extensive than the previous brief overview of the

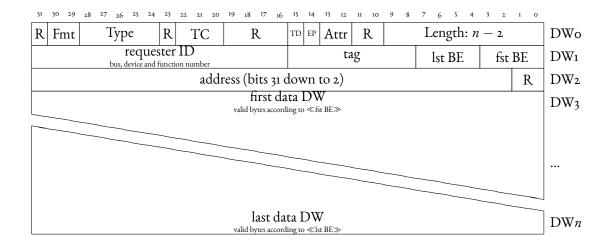

Figure 2.3: PCI Express MWr TLP, created after [10]. Format (labelled «Fmt») and type define the length of the TLP header, the TLP type and whether the TLP carries data. Requester ID and tag form the transaction ID through which errors can be relayed back to the requester. The address is always specified as 32 bit-aligned, which is why the last two address bits are reserved. All reserved fields (marked «R») must be set to 0. «Length» specifies the data length in DWs which is 3 DW less than the total length of the TLP.

physical and data link layer. Other than the previously described physical and data link layer protocols, which describe behaviour on a single link between two ports, the transaction layer protocol describes the routable topmost layer of the PCI Express protocol. This means that a TLP will travel across a number of links from one sending endpoint to one or more receiving endpoints. As the name suggests, a sequence of one or more exchanged TLPs is used to implement logical transactions like e.g. «write 0x123456ab to address 0x08154711».

### 2.3.1 Posted and Non-Posted Transactions

As suggested by the preceding paragraph, PCI Express transactions are conducted via the exchange of packets. Transactions can be one of two types, either posted or non-posted. Generally all transactions are initiated by a request. The initiating party sending the request is called the «requester».

Posted transactions usually comprise only one packet and are finished once this packet is successfully received. A posted request requires no answering packet, except if an error occurs. An example would be a «memory write» transaction, with the memory write request containing all necessary address and data information to execute the transaction. An answer is unnecessary, because success is assumed if no error is explicitly signalled.

Correspondingly, non-posted transactions are transactions which require an answer in both, successful and unsuccessful, cases. The request issued by the requester has to be answered by a so-called «completion». Accordingly, in all transactions, the second party is called the «completer» in PCI Express parlance. An example would be a «memory read» request which must be «completed» —i.e. answered— with the requested data that was read.

### 2.3.2 TLP Types and Organisation

TLPs consist of a header sometimes followed by data, depending on their type. The PCI Express specification commonly uses the term «doubleword (DW)» to denominate the size unit in which TLP sizes are given. A DW is 32 bit —or 4 byte— long, consequently TLP header, data and total sizes are always integer multiples of 4 byte.

Headers may be 3 or 4 DW in size. In all TLP types, the first DW of the header has the same layout, specifying the type of the TLP, the header size, whether the TLP contains data and the data length. Attributes to indicate the traffic class used for prioritizing TLPs in routing, an «error poisoned» bit to mark a damaged TLP and an attribute to control cache coherency are also present. The interpretation of following header DWs depends on the type of the TLP.

TLP types can be classified by various criteria. The difference between requests and completions has already been discussed in section 2.3.1. Completions are further differentiated into «completion with data (CplD)» and «completion without data (Cpl)». The former is used to return data from successful non-posted requests, the latter is usually used to signal error conditions or to complete non-posted transactions which do not return data.

Requests are classified into reads and writes as well as by the target memory or register type. The latter stems from the different semantics of transactions pertaining to configuration and I/O space. The most commonly used, are of course «normal» memory requests, «memory read (MRd)» and «memory write (MWr)». Message TLPs can be used to signal interrupts as well as a number of other conditions. Because they are not important for the scope of this work they will only be mentioned for the sake of completeness and not discussed in depth. As a legacy mechanism, several types of locked transactions are specified. We will also skip further description of such locked type TLPs as the PCI Express specification forbids non-legacy endpoints from supporting them, rendering their discussion unnecessary for this work.

#### Memory and I/O Requests

Memory and I/O request headers are identically structured due to the fact that they all address a certain area of memory. The header always ends with the address the request refers to. Because PCI Express supports memory requests with 32 bit and 64 bit address widths, the corresponding request headers may be 3 or 4 DW long, respectively. Endpoints are recommended to support 64 bit addressing. In each case, the last or lowermost two address bits are always reserved and set to zero. This stems from

the fact that all requests have to be aligned to 4 byte boundaries. Unaligned or smaller requests are possible by specifying a «byte enable» bitmask in the second DW of the request header.

To match a request with its corresponding completion, the second header DW also contains a 2 byte requester ID and a 1 byte «tag». The concatenation of the requester ID and tag forms the transaction ID. The tag is used to uniquely identify the transaction among all open transactions of a requester. This means that one requester can have at most 256 open transactions<sup>2</sup>. The requester ID is composed of bus, device and function number. These numbers correspond in function and form to the PCI-IDs. They are assigned to each device at boot or initalisation time by a configuration process.

#### Completions

Completions are required to conclude non-posted transactions. Typically, non-posted transactions are all memory transactions that are expected to return data, i.e. memory reads. Also, I/O read and write transactions require completions, even if no data is returned. Errors for posted requests are also signalled by completions.

All completions have the same header layout, regardless of whether they carry data. To identify the corresponding transaction, the transaction ID from the original request is included, consisting of requester ID and tag. In layout and function identical to the requester ID, the ID of the completer is included as well. Three completion status bits signal if the completion is considered successful or if the request could for some reason not be completed, e.g. because the type of request is unsupported or because the completer lacks resources to fulfil the request.

A single request may be answered by multiple completions. This may happen if a memory read requests a larger amount of memory which the completer is not able to provide in one piece. To support such types of completions the header includes a «lower address» field, indicating the lower address bits of the returned data, and a «byte count» field. This field indicates the number of remaining bytes that still need to be transmitted for a successful completion of the transaction. It is required that the partial completions arrive in an ordered fashion, so that addresses of the transmitted data portions are always ascending. Completions without data ignore all these data-related fields.

#### Other TLP types

There are further TLP types to transmit messages of various kinds and to be used at configuration time to set the configuration registers of endpoints. These types are more varied and have a wide range of semantics. An in-depth discussion of them will not be provided here for reasons of brevity. An understanding of them is not necessary for the purposes of this work.

<sup>&</sup>lt;sup>2</sup>Usually only 32 transactions may be open, using only the lowermost 5 bit of the tag. The number of open transactions for a requester can be extended by various means if necessary, e.g. by using the whole tag field, leading to the mentioned 256 open transactions. For the scope of this work, the standard amount of 32 to 256 is more than enough.

## 2.3.3 TLP Routing

Depending on the TLP type, there are several ways for a PCI Express switch to decide how to forward a given TLP. TLPs that include a memory address, e.g. memory and I/O reads and writes, are routed by inspecting that address. Completions are routed via their included requester ID back to the requester. Messages provide both these routing methods as well as some special routing methods like «broadcast», depending on the message type.

### 2.3.4 Transaction Timing and Ordering Requirements

PCI Express uses a transaction protocol where the request and the corresponding completion or completions ending the transaction are separate packets. This packet-based approach leads to some important questions. The answers to these questions directly influence whether the goals set for this work are achievable.

As was discussed earlier in section 2.3.2, each endpoint is allowed a certain number of open requests, i.e. transactions that are not yet completed. The rather large number of open transactions allowed directly leads to the question of whether all those transactions must be completed in a certain order and whether a completer might issue its own requests having transactions yet to complete.

The specification defines certain ordering requirements to ensure that deadlocks do not occur. Most importantly, completions to read transactions should be processed before processing any new non-posted requests. Also, posted requests should be processed before non-posted requests. This leads to two important conclusions: The opportunity for a deadlock is only present if the completion of a transaction by the completer depends on the completion of a request issued by that completer. This means that the idea of transactions depending on the completion of another transaction was known to the writers of the specification and the specification has been written to allow such behaviour. It is completely acceptable to process transactions in the order they arrive in, only giving precedence to incoming completions over incoming requests to avoid having to track the state of multiple uncompleted transactions internally.

The actual ordering requirements in the specification are a little more elaborate, especially since they also define requirements for configuration, message and I/O TLPs that will not be handled by the implementation of this work.

Knowing that transactions may depend on the completion of other transactions issued by the completer of the outer transaction begs the following question: How long may the completion of a transaction take and how long may the internal data processing on the FPGA take?

The PCI Express specification defines a completion timeout mechanism. This mechanism defines the behaviour of an endpoint or the root complex if an expected completion does not arrive in time and a maximum and minimum acceptable definition of  $\ll$  in time $\gg$ . The timeout event must not occur in less than 50  $\mu$ s. It must not take longer than 50 ms to occur and, except if there are strong requirements to the contrary, at least 10 ms are recommended. The timeout event generates an error report by the

requester and the time is tracked by the requester. This means that the complete forwarding delay through the PCI Express bus also adds to the measured transaction time. Each requester may define its own timeouts within the given range, depending on its requirements.

In this work, the FPGA uses a clock frequency of 100 MHz, meaning that one clock cycle is 10 ns long. This means that the absolute upper limits for processing a request are of the order of  $5 \cdot 10^3$  to  $5 \cdot 10^6$  clock cycles. In reality this will of course be somewhat shorter to allow for buffering and forwarding delay. Given that for example encryption algorithms usually take only in the order of tens<sup>3</sup> of clock cycles in FPGA implementations, there is the realistic expectation that such transformations are possible within the given time. Especially if the root port as the most common or only requester in our case does not implement the strictest possible timeout requirements, the time a transformation takes should be completely negligible compared to the allowed timeout.

Furthermore, nested requests should also be possible within the timeout range, because if the timeout requirements were too strict for such nesting, bridges to other, slower bus systems and deeper hierarchies of switches would quickly run into problems.

## 2.4 DMA and Device Memory

Between a PCI Express endpoint and the software running on CPU and main memory there are two possible memory domains and directions for memory accesses.

Coming from and initiated by the software on the CPU, device memory can be accessed. Device memory is a memory area assigned to a specific endpoint for which that endpoint handles accesses. Device memory is configured using the so-called «base address registers (BARs)». In PCI Express terms, device memory accesses are accesses where the completer for a memory transaction is an endpoint and the requester for that transaction is the root port<sup>4</sup>.

In the other direction, coming from and initiated by an endpoint, a computer's main memory can be accessed. These accesses can happen without interrupting normal program flow of the software running on the CPU. Such accesses are commonly known as «direct memory access», or short «DMA». In PCI Express terms, DMA accesses are memory transactions where the requester is an endpoint and the completer is the root port.

### 2.4.1 Base Address Registers

PCI and PCI Express devices are configured at boot time or when they are initialised after having been plugged in. In an enumeration process, endpoint IDs are assigned and configuration registers are initialised. In this phase, base address registers are programmed.

<sup>&</sup>lt;sup>3</sup>As we will later see, the AES128 encryption core used in this work takes 13 cycles plus 2 more for loading input data and keys.

<sup>&</sup>lt;sup>4</sup>Device memory accesses from and to other devices are possible, but seem to be uncommon.

Base address registers —commonly known by their acronym «BARs»— describe the memory and I/O areas within a PCI or PCI Express endpoint. The operating system or BIOS manipulates configuration registers through «configuration write» or «configuration read» transactions. To configure a BAR, the endpoint requests a certain amount of address space with the desired properties like prefetchability<sup>5</sup>, address width<sup>6</sup> and type. The BAR type may be either «memory», meaning that the address space configured by that BAR is a «normal memory area» which can be written or read by the usual memory transactions. Alternatively, the BAR type may be «I/O», meaning that only I/O transactions with special semantics are required to read and write values from that area. The use of I/O space is discouraged by the PCI Express specification.

The size and other properties are encoded into a 32 bit or 64 bit data word. That data word is read<sup>7</sup> from the endpoint register by the configuring software and the assigned address space base address is written into the register. PCI configuration space contains 6 BARs, usually named BARo through BARs. Those BARs have a width of 32 bit. 64 bit BARs are formed by concatenating adjacent BARs, meaning there may be at most 3 of 64 bit wide BARs.

The address space assigned through a BAR may be handled by the endpoint in various ways. One possible way is the use of physical memory modules addressed by that BAR address space. The most obvious example for such use is the memory residing on a graphics card, containing a framebuffer, shader programs or textures that the graphics driver can read and write at the mapped address space location. In other cases, the BAR memory area may be mapped to configuration registers with special semantics controlling the internal workings of the endpoint device. Almost every device has at least one such BAR for interaction with driver and application software. In this work a third way will be used where the endpoint does not provide any physical means of storing the data in the BAR memory area. Instead, the memory area is used as a means to map requests onto a DMA main memory area, providing only a «transformed view» onto that DMA area.

Sometimes the denotation «BAR» is used not only for the register in configuration space but synonymously with the area of device memory configured using that configuration space register. So one might for example say «The packet to be transmitted is written to BAR3», meaning that the packet will be written to the device memory area configured in the fourth base address register. Such use should of course be avoided where it may lead to confusion. For this work, I will prefer the more precise terms «device register space» or «device memory space».

<sup>&</sup>lt;sup>5</sup>A memory area is considered prefetchable, if read operations do not have side effects and if multiple write operations may be merged into one larger operation. This allows for read-ahead and delayed-write caching, hence the word «prefetchable».

<sup>&</sup>lt;sup>6</sup>Available address widths are 32 bit and 64 bit.

<sup>&</sup>lt;sup>7</sup>Actually the process of reading the requested values is a little more elaborate, but the details are of no consequence for this work.

### 2.4.2 Direct Memory Access

Configuration of DMA memory is specified in far less detail than accesses to device memory via BARs. Generally, every physical address addressable over a bus system is reachable to a requesting endpoint. Yet there are some exceptions from this general rule of accessibility that need to be discussed in detail.

An «IOMMU» is a device similar to the «memory management unit (MMU)» found in all modern desktop and many embedded processor architectures. The MMU of a processor translates between configurable address space layouts by mapping physical and logical memory pages, segments or addresses. This means that by mapping or not mapping a certain page or segment into the logical address space of a process, this process can be allowed to or prevented from accessing this specific page respectively. Furthermore, the types of access to a memory area can usually be defined, that is whether reading, writing or execution is allowed. While an MMU fulfils this role for accesses between CPU and main memory, an IOMMU does the same for accesses from and to devices and device memory. As such, an IOMMU may prevent an endpoint from accessing memory outside its assigned DMA area. Therefore, in order to find a suitable DMA area for a device, the IOMMU, if the system is equiped with one, needs to be configured to allow access to the chosen area. In the other direction, the IOMMU may prevent a software program or another device from accessing device memory not assigned to it.

Because IOMMUs are not available in legacy systems and in many systems on sale today, this means that a PCI Express endpoint may read and write almost all available physical memory without limitations. Even without an IOMMU, there may be areas of memory unavailable to a PCI Express endpoint. Usually this happens when an endpoint only supports 32 bit transactions on a 64 bit system with a sufficient<sup>8</sup> amount of main memory. In that case, there will be physical addresses that are not addressable for the endpoint. For the configuration of DMA that means that the DMA area needs to be located in the part of the physical 64 bit address space that is mapped to the 32 bit address space.

Also, depending on the cache hierarchy of a processor architecture and its configurability and locality with respect to the PCI Express root port, there may be necessary configuration settings such as cache behaviour and constraints such as unusable areas for DMA. An operating system therefore needs to find, configure and assign<sup>9</sup> DMA areas to devices requesting such areas.

After the operating system has chosen and configured a suitable memory area, the way to transmit the information necessary to access that area to the device is device-specific. The easiest and most common way is for the endpoint to provide one or more registers in the device register space. The device driver writes the start address and either length or end address of the DMA area to the appropriate device registers. This practice will also be followed in this work.

<sup>&</sup>lt;sup>8</sup> «Sufficient» memory means  $2^{32}$  B = 4 GB, the amount addressable by a 32 bit address space.

<sup>9</sup>Some classes of devices support a mode of operation known as ≪scatter-gather-I/O≫ where no fixed DMA area exists. Examples of such devices are certain network interface cards which can assemble network packets for transmission from multiple memory locations containing only parts of a packet like various layers of headers and the data payload. Those special cases will not be discussed.

## 2.4.3 Cache Behaviour

There are several mechanisms which can be used to control cache behaviour in PCI Express. They differ depending on whether DMA or device memory is involved.

Caching for DMA memory is configured by the operating system with appropriate flags in the page or segment descriptors of the relevant memory pages. The Linux kernel API provides us with mechanisms to do this, which will be described later on in chapter 4. Because the endpoint needs at least some control over the cache presence and coherence of its DMA memory, the PCI Express specification defines special semantics for a memory read with a length field of zero: Such a zero-length-read is supposed to initiate a cache flush. When the completion to this flush request arrives, the memory area should be in a consistent state.

Memory transactions also contain a «no snoop» bit. Setting this bit indicates that, according to [10] «[h]ardware enforced cache coherency [is] not expected» for this transaction. While the PCI Express specification does not specify further what the exact semantics should be, I understand this to mean that e.g. writes with the «no snoop» bit set would not be immediately visible to the CPU if an old version of that portion of memory were in the CPU cache. Setting the «no snoop» bit would prevent measures for cache synchronisation from being performed[12].

For device memory the «prefetchable» option, configured through a bit in the BAR, offers some control over the caching behaviour. If a device memory area is configured to be prefetchable, read or write accesses must not have immediate side effects. Such side effects are typical for BARs refering to device register space, where e.g. writing a certain register address might cause the endpoint to initiate an immediate reset. Therefore a device memory area where such side-effects are implemented should not be set prefetchable. If no side-effects are implemented, prefetchability will improve performance e.g. by allowing the CPU to issue read requests for larger amounts of data than immediately needed and caching the returned data.

## Chapter 3

## **FPGAs**

## 3.1 FPGAs as Programmable Hardware

### 3.1.1 Definition

«Field Programmable Gate Arrays (FPGAs)»[13, 14] are configurable arrays of logic elements. By configuring them, within certain limits of course, arbitrary circuits can be created, re-created and changed. Reconfiguration of an FPGA is possible within a few seconds, meaning that development cycles for FPGA hardware are very much shorter than for «ordinary» hardware that has to be soldered, etched or fabricated in other time-consuming processes. While the speed and ease of hardware development using FPGAs is still not on par with the development of software, certain applications may justify the effort.

The basic building blocks of FPGAs are «lookup-tables (LUTs)», «multiplexers (MUXes)» and a configurable interconnect fabric. Lookup-tables are memory-elements with n outputs and an m-bit selection input. For each of the  $2^m$  select input states, an output state is programmed into the memory element. Upon encountering such an input state, the respective output state is assigned to the output lines. A multiplexer is an element with n selection inputs,  $2^n$  data inputs and one data output. For each different state of the selection inputs, the corresponding data input line is connected to the data output line. Together¹ both of these types of elements can be used to recreate any existing boolean logic function of a certain number of inputs and outputs. These functions are then strung together by the configurable interconnect fabric. Usually this fabric is a grid of connections that can be connected by programmable fuses at the startup of the FPGA. Clock distribution networks and additional clock inputs to the logical elements mentioned above provide the means for implementing clock-synchronous logic.

<sup>&</sup>lt;sup>1</sup>MUXes and LUTs are very similar in their nature and can be transformed into each other. Therefore it is not really important for the user of an FPGA how the vendor implements the hardware.

CHAPTER 3. FPGAS

FPGAs often provide additional capabilities beyond the implementation of arbitrary boolean logic, for example input and output pins with programmable electrical characteristics, analog elements like ADCs, embedded processor cores or bus interfaces.

## 3.1.2 Availability

Various hardware platforms are commercially available that include FPGAs as coprocessors[15], on add-on cards[16] or are FPGAs with embedded processor cores. The prices[17] for FPGA chips are currently, for the model used for this work, well below \$ 100, for certain models and in larger numbers even below \$ 100. Larger models are of course more expensive, but also more capable.

FPGA add-on cards are available in various price-ranges and sizes and for different applications, e.g. as coprocessors for high-performance computing applications or as development boards providing the means to easily develop custom hardware prototypes. The Raggedstone2 board from Enterpoint[16] is one such development board that is used in this work.

## 3.2 Hardware Description Languages

On the lowermost level, electronics are made of transistors and wires, out of which logic gates, flip-flops and other higher-level structures are formed. In a trend whereby the complexity of larger circuits is managed via higher levels of abstraction, the current state of the art in circuit design utilises «hardware description languages (HDLs)». Three HDLs, «VHSIC hardware description language (VHDL)», «Verilog» and «SystemC» are currently in widespread use.

### 3.2.1 VHDL and Verilog

Because VHDL[18, 19] and Verilog[20, 14] have been used in certain parts of this work, this chapter will outline the most important characteristics of those languages.

For the understanding of this work, a knowledge of the syntax of VHDL and Verilog is of course beneficial, but it is not my intention to teach<sup>2</sup> the reader any of those languages. Instead I will describe the terminology, programming model and the semantics that both languages share, as far as they are relevant to the understanding of the implementation. The terminology used will mostly reflect that found in VHDL and software development. The reader will also find all these concepts in Verilog as well, just perhaps under a different name.

### Modelling of Time, Sequence and Causality

In most popular software programming languages, time is modelled mostly by the linear sequence of lines of code. In line n it is guaranteed that line n-1 has been executed and all changes up to line n-1

<sup>&</sup>lt;sup>2</sup>For an introduction into VHDL or Verilog see e.g. [18] or [14], respectively.

have been performed. Loops and jumps simply reorder this strictly linear sequence of lines by deciding which line gets to be n + 1. This linear equivalence of time and lines of code is of course derived from the linear sequence of instructions the CPU executes. Time is understood to progress with the linear sequence of instructions, although there is typically no fixed amount of time per line of code. Line n is just understood to be executed after n - 1.

In HDLs, linearity is only available where explicitly introduced by certain language constructs, everything not explicitly linearised is by default executed in parallel. Sequencing can be introduced in two ways: Either by data dependence together with the use of immediate assignments, this is called «asynchronous»; or sequencing is achieved by synchronising the execution of statements or blocks of statements to a clock signal, this is called «synchronous». A combination of both techniques is common. A block (in VHDL a «process») is triggered by the rising edge of the clock signal. Inputs to that block are expected to be valid at that point in time. All computations in that block are executed in parallel or sequence depending on their data dependence, yielding results. Those results are expected to be valid no later than at the next rising edge of the clock so they can be used in the same or other processes for further computations.

#### Entities

Entities are independent modules. Each entity consists of its «ports» or «pinout» and its «architecture» or «implementation». Input and output ports are often referred to simply as «inputs» and «outputs». The most fitting image is of course that of a microchip with a number of pins with certain characteristics and functions that the user of a chip has to worry about when designing a board with it. The producer of the chip has the additional task of providing the implementation: the inner workings of the chip.

In quite the same way, an entity with a given set of ports may be used as a black box, the implementation to be filled in later from a netlist file or a hard-IP part of the FPGA. Alternatively the implementation of the entity may be provided by the programmer, using the entity as a means of encapsulation.

#### Data Types and Variable Types

Like in software programming languages, HDLs have the basic concept of data types. One may, for example, declare something an «integer» or «float»<sup>3</sup>. The most common type used in digital circuits is of course the «bit» and one-dimensional arrays thereof. Although for example the most common VHDL data type «std\_logic» used as a bit type is actually an enumerated data type with nine possible values, the seven «other» values are rarely used. In almost all situations it is sufficient to consider «std\_logic» to be one bit.

<sup>&</sup>lt;sup>3</sup>The actual names of the available data types may differ from these examples depending on the language, its version and the library package in use

26 CHAPTER 3. FPGAS

«Variable types» are a concept that is unknown in the field of software programming. While a data type describes the form of data that is stored or transmitted, the variable type describes whether a piece of data is stored or transmitted. To understand the difference, one needs to look at the two things that can happen to data in a piece of hardware. The data can be stored, in a register or a similar storage element, or it can be transmitted over a wire. As one often simply «wires up» existing modules, the transmission of data between these modules is essential. Introducing storage elements in between two modules would add delays and possibly change timing behaviour of the circuit so that performance would suffer or necessary timing constraints would not be met, making the circuit non-functional. Therefore control over the introduction or non-introduction of storage elements into a circuit is very important.

Verilog calls its two variable types «wire» and «reg» in accordance with the explanation provided above. VHDL deviates from this naming as well as from the semantics. In VHDL, a «signal» is roughly the equivalent of a wire, a «variable» is almost the same as a «reg» in that the usual roles of being a storage element or a transmission element are similar. The main differences lie in the assignment semantics of both languages.

Verilog provides the operators «=» and «<=» for «immediate» or «blocking» and «delayed» or «non-blocking» assignments, respectively. An immediate assignment is visible in the next line of code, similar to the usual assignment semantics in software programming languages. A delayed assignment will be executed at some future time, in simulations at the next simulation time increment, in hardware some time before the next clock cycle.

VHDL also has immediate and delayed assignment operators, «:=» and «<=», but those are only allowed to be used with one variable type each. Immediate assignment may only be applied to variables, delayed assignment may only be applied to signals. In other words, the lvalue for «:=» must be a variable, for «<=» a signal. Therefore the more common terms for such assignments are variable and signal assignment.

While this may seem like a reduction in functionality compared to Verilog, VHDL signals and variables are not exact equivalents of Verilog's wires and regs. While in Verilog, a reg will always generate a storage element, where a wire will never do so, in VHDL both signal and variable may create either a connection, a storage element or both, only depending on the assignment semantics. This means that to create an output port where a driver holding the signal to be output is necessary, one always needs to create a combination of a wire and reg in Verilog, where the reg is the driver holding the data and the wire is the transmission line. In VHDL, using a signal as output is sufficient, the necessary driver is created automatically.

There are several further small differences between Verilog and VHDL in this area, but those are of lesser importance.

## 3.2.2 Compound Data Types and Other Niceties

The support for more complicated data types than bits and bit vectors is often lacking in many implementations. Two of these types were used in this work where convenient: integers and record data types. Integers are transformed into arrays of bits by the synthesis tool, with implementations for adders, comparators and similar inserted to support the arithmetic operations used.

Records are used to group and structure input and output ports which would otherwise consist of a large number of single bits and bit-arrays. A common example is a parallel bus system, which defines a large number of data and control signals like «ack», «busy», etc. Using a record type for that bus allows a bus connection to be created in one line, where otherwise a large amount of redundant declarations would have been necessary. In addition to the readability and writeability improvement, maintenance of the code is simplified. New signals can be added to a bus by changing a common file where the record type is defined instead of changing every file where that bus type is used.

Given that record types only containing std\_logic and std\_logic\_vector types are no more than a convenient renaming of their members, there is a surprising number of warnings concering possible problems, but also some endorsement[21]. Consequently, there seem to be only few projects and standards, for example on OpenCores[22] using record types. Because no major problems, only some minor inconveniences, have been observed, this work uses record types extensively.

### 3.2.3 Implementation of State Machines in HDLs

Most of the implementation in HDLs in this work consists of state machines. The implementation of state machines is a very basic technique for implementing hardware functions. Generally, the definition of a state machine in this context involves four necessary parts: First, the enumeration of possible states, second, the possible transitions between these states, third, the constellations and conditions of inputs under which these transitions take place and fourth, the outputs or more generally the actions happening in each state.

From the view of a software programmer, these parts of the definition provide perfect division lines along which the implementation may be structured. For example the second part might be encapsulated in a decision function taking all inputs and the current state as a parameter and returning the next state. The fourth part, the actions and outputs of each state might be implemented as an execution procedure for each state. One VHDL process might be used to encapsulate the decision function or the execution procedures

Yet the characteristics of HDLs discussed above make this separation of the various concerns impossible: The aforementioned variable or assignment types force a common scope for assignments. If one wishes to avoid this common scope, additional registers and wait-states need to be introduced and data needed for outputs as well as decisions for state transitions need to be duplicated unnecessarily. This unfortunately means that the implementation will use one process per state machine, containing all decisions, inputs and outputs within the same code parts.

28 CHAPTER 3. FPGAS

## 3.3 Toolchain

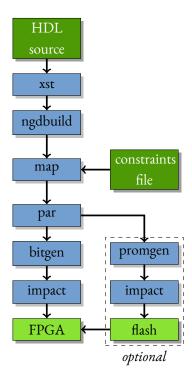

Figure 3.1: Build process used to program the FPGA from HDL source code. The alternative optional path can be used to permanently program a flash memory chip which programs the FPGA on each powerup.

To translate the HDL source code into a bitstream which can be loaded into an FPGA, a multi-stage toolchain is employed. For use with Xilinx FPGAs, Xilinx provides a software suite called «ISE». While other toolchains are available, ISE has been chosen for being free and naturally most suitable for use with Xilinx hardware.

In a first stage, called «synthesis» the HDL sourcecode is translated into a so-called «netlist». The netlist represents the behaviour of the HDL source in terms of interconnected generic components like state machines, memory or logic gates. The command-line version of the synthesis tool is named «xst».

The second and third stage with the tools «ngdbuild» and «map» assign concrete components that are specific to the target FPGA, where the output of xst only contained generic components. Highlevel generic components like state machines are decomposed into lower-level components. Also, the constraints such as the location of I/O pins are incorporated into the netlist. Constraints are specified

3.4. IP CORES

via a special constraints file, but it would also be possible to annotate constraints within the HDL source if necessary.

Fourth, in the place & route stage, the «par» tool assigns fixed locations on the FPGA to all components which have not already been assigned a location earlier by constraints. Signals are routed between these resources with respect to timing constraints. The place & route stage is usually an iterative process where, starting from an initial non-optimal solution, the placement and routing is incrementally improved until timing constraints are met.

The information is then transformed into a format suitable for loading into the FPGA by the «bitgen» tool. The resulting bitstream can either be loaded directly into the FPGA by use of the «impact» programming tool, or the bitstream can be converted into a flash file format. This flash file can then be loaded onto an onboard flash-memory-chip that automatically programs the FPGA on power-up. Programming the flash memory is usually done for the delivery of a finished product. During development the FPGA is loaded directly to conserve time and limit flash write cycles.

### 3.4 IP Cores

$\ll$ IP cores», with  $\ll$ IP» standing for  $\ll$ intellectual property», is a common denomination for available building blocks a hardware design may incorporate. Often the designation is shortened to just  $\ll$ IP». For a software developer the usual analogon would be software libraries, which can be linked to a software design and provide the desired functionality. IP cores can be classified into two main categories,  $\ll$ soft IP» and  $\ll$ hard IP».

Soft IP consists of HDL source or netlists included in the appropriate place by the toolchain. Its functionality is then provided by use of the usual FPGA primitives, like any other piece of HDL code. Typical examples for soft IP are interconnect busses for slower bus systems that do not require elaborate physical interfaces like Wishbone[23], or implementations of algorithms like matrix operations, video encoders or DSP functions.

Hard IP on the other hand consists of primitives already available on the FPGA, usually because their implementation in terms of the usual FPGA primitives like multiplexers and fuses is impossible or too resource intensive. An example of such hard IP is the high-speed serial interface necessary to support PCI Express on an FPGA: Typical FPGA hardware would not be able to handle the required high clock frequencies in the 2 GHz range. For that purpose, the Xilinx Spartan 6 FPGA used in this work has a builtin serial interface hard IP that can, among other things, be used as a PCI Express physical interface.

### 3.4.1 «Xilinx PCI Express Endpoint Block» core

In the implementation, a Xilinx IP core[24] is used to provide a basic PCI Express interface.

The Xilinx PCIe Core provides a 1-lane PCI Express interface compliant to version 1.1 of the PCI Express specification. The core is able to handle the physical interface and the DLLP completely. With

30 CHAPTER 3. FPGAS

respect to the transaction layer protocol, the core handles all configuration requests by implementing the required PCI-compatible configuration space as well as some extensions and extended capabilities. TLPs other than configuration TLPs are passed to the user-implemented application<sup>4</sup>.

Two internal on-chip interfaces are provided, an older variant called «TRN» as well as a newer one intended to replace TRN, called «AXI». In this work, the TRN interface was used. While there are differences between these interfaces, they mostly concern details like line polarity and the naming of signals. Line polarity determines whether a high voltage should mean a logical «true» or «false». Usually these polarities are called «active-high» and «active-low» respectively. Some consider active-low polarity, where an electrical «1» represents a logical «0» to be poor style because of lower readability and possible confusion. Standards like «Wishbone»[23] that are used in the implementation make similar arguments, therefore all signals in this work will be implemented as or converted to active-high. With the AXI interface using active-high polarity in almost all signals as well, most of the conversion from TRN to AXI has therefore already been done internally, the remaining differences should be quick to resolve if necessary.

### 3.4.2 ChipScope core

Additionally, IP cores for the Xilinx «ChipScope» debugging system have been used during development. ChipScope allows, among other possible functions, to embed a virtual on-chip logic analyzer which can be used to monitor internal states which would have been unavailable or hard and expensive to monitor with external instrumentation. Because ChipScope only consists of an IP core and a software component, its use only requires reprogramming the core instead of obtaining an expensive logic analyzer and attaching external probes after routing all internal signals to output pins of the FPGA.

#### 3.4.3 AES128 core

The AES128 encryption used for the encryption example is an IP core from OpenCores[22] written by Hemanth Satyanarayana. The core has been published as open source under the «LGPL v2.1 or later» license, is well written and usable with only very minor adaptions.

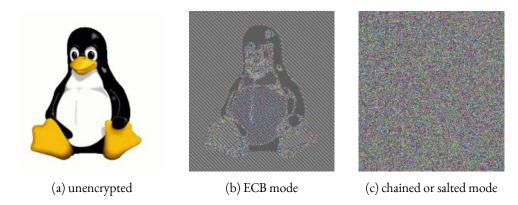

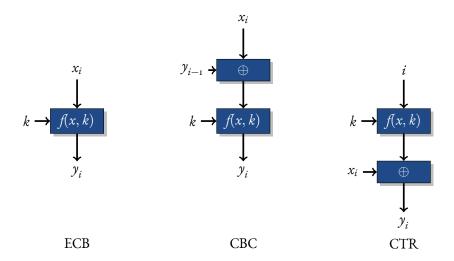

The documentation included in the core source code states a 13 cycle processing time after loading the key and data registers. This means that within 15 cycles, also accounting for input and output cycles, one block of data can be encrypted. The core itself implements only the trivial ECB block cipher mode, which has been extended as described later on in section 4.6.

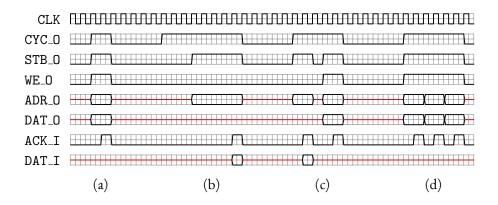

Figure 3.2: Examples of synchronous Wishbone Classic cycles. Signal directions are as seen from the master, meaning the master drives all signals with \_0, the slave drives all signals with \_1.

(a) shows a simple single write cycle, which is completed as fast as possible. (b) shows a read cycle, where the master as well as the slave each take a few cycles of time to output the address the master would like to read and to answer with data from the slave. In (c) a cycle containing two transactions, first one read, the a write is shown. As shown in (d), the fastest possible transmission of data with Wishbone Classic synchronous cycles is one transfer per two clock cycles. Red lines signify undefined states that are ignored by all interfaces.

### 3.5 The Wishbone Bus

The Wishbone bus[23] is a standard for on-chip connections between IP cores. It is most popular among Open-Source communities like OpenCores[22]. A sigificant part of the free and Open-Source IP cores provided there feature Wishbone-compliant interfaces. So while one reason for its use is the availability of compatible components, the other reason is that the specification is well thought-out and easy to use. A sensible set of signals for the transmission of data with defined timing and semantics is provided.

Wishbone being an on-chip bus system, the specification does not define any physical signal requirements. Any definitions and requirements are based on the assumption that there is a stable clock as well as the means to transmit logical states available. Because these assumptions hold for an FPGA it is of course possible to implement Wishbone-compliant connections on such devices. There is no required topology for Wishbone interconnects, the standard is flexible enough to allow for point-topoint, switched, shared-bus or sequential/pipelined arrangements. In our case simple point-to-point connections will be used, therefore a discussion of the more complicated variants will be skipped.

<sup>&</sup>lt;sup>4</sup>The terminology «application» is used throughout the Xilinx documentation and code, usually meaning «what the user of a core implements utilizing the core». Keeping with this terminology, the parts of the FPGA software that are intended to be replaced or modified by the user are called application or «app».

CHAPTER 3. FPGAS

Wishbone interfaces can be implemented in one of several modes, depending on the performance and implementation complexity requirements. Only one of these, the synchronous variant of the Wishbone «Classic» transfer mode will be explained here, as it will be used in the implementation.

All signals in Wishbone are active-high, meaning that an electrical  $\ll$ high $\gg$  voltage state is equivalent to a logical  $\ll$ true $\gg$  or  $\ll$ 1 $\gg$  state. The direction of each signal is indicated by a suffix, outputs are named with the suffix  $_{\sim}$ 0, inputs with  $_{\sim}$ 1.

Interfaces can be of one of two types, «master» or «slave». In any system there must be at least one master and one slave interface. A master is capable of initiating a «bus cycle» by asserting its CYC\_O output. The arbitration logic of e.g. a switch or shared bus interconnect may use this signal in the arbitration process. The slave has a corresponding CYC\_I input which, when asserted, causes the slave to evaluate the rest of the inputs of its Wishbone interface.

In a cycle, the master may make requests to the slave by asserting the STB\_O signal and simultaneously setting the appropriate address, data and write enable bit to ADR\_O, DAT\_O and WE\_O. The data is only necessary if the data is to be written, when reading DAT\_O from the master is ignored. The master keeps STB\_O asserted until the slave acknowledges the completion of the request by asserting its ACK\_O. When the request was to read data, the slave simultaneously outputs the data on its DAT\_O. The ACK\_O signal stays asserted for one clock cycle per unit of data transmitted. This means that if the master keeps its STB\_O asserted after receiving an acknowledgement on its ACK\_I, this constitutes a new request.

The specification provides other modes and further signals to transmit data faster without waitstates, signalling errors, locking the bus for exclusive access and more. As these are not used in this implementation their discussion will be skipped.

## Chapter 4

# **Implementation**

The following sections are arranged in an approximately chronological order. I will describe my progress in the implementation of the overall project as well as the occurring problems and dead ends.

## 4.1 PCI Express FPGA Card

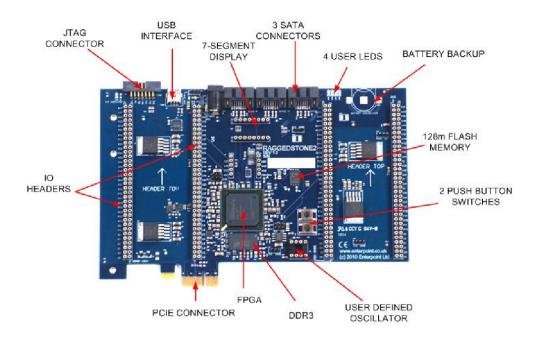

Figure 4.1: Photography of the Enterpoint Raggedstone2 FPGA PCI Express development board. From [16].

The PCI Express FPGA card used for this work is a «Raggedstone2» board (see figure 4.1) by Enterpoint[16, 25]. The main component of the card is a Xilinx «Spartan-6 XC6SLX45T-4FGG484C» FPGA. The PCI Express card has, in addition to the standard 1-lane PCI Express connector, a large number of IO pins for extension modules as well as several LEDs and switches. Three SATA and an USB connector, some RAM and a flash memory module are also available. For this work, only the LEDs were used to signal internal states of the FPGA for debugging purposes. Programming of the FPGA and flash memory is done via the JTAG port using a compatible programmer.

## 4.2 Xilinx PCI Express Endpoint Core

Xilinx provides, through its «Core Generator» application, two variants of a PCI Express interface core, named «Spartan-6 FPGA Integrated Endpoint Block for PCI Express»[24]. For the sake of brevity, I will abbreviate the name to «Xilinx PCIe core» or «core» where appropriate. As mentioned in section 3.4.1, several versions of the core exist, differing in their on-chip bus interface. Also, each new ISE revision seems to ship a new revision of the core.

The core is configurable through the Core Generator application, where details concerning e.g. the PCI configuration space like the PCI-IDs and the configuration of the BARs can be set.

Together with the core, a constraints file specifying relevant timing and pinout constraints as well as an example application implementing device memory are provided. In an application note[26] an example DMA application together with some benchmarks and related tools is also provided.

## 4.3 First Tests with the Example Application

In a first attempt to familiarise myself with the Xilinx PCIe core and to verify the correct function of the RaggedStone2 card and the computer system in which it was installed I tried to recreate the example mentioned in the RaggedStone2 documentation[25]. First attempts were unsuccessful due to a very strange behaviour of the computer system containing the card: no PCI Express devices where recognised in the Fujitsu-Siemens Esprimo P5915 system used, no matter which kind of PCI Express card was plugged in. The «lspci» tool as well as the linux kernel log showed no sign of any PCI Express devices being present, besides those that are part of the mainboard chipset. I can only speculate about the reasons for this behaviour, the most plausible one being that the single PCI Express slot in the system is intentionally limited to the use with a DVI adaptor card for the on-board graphics chip.

Using a newer and more capable Fujitsu-Siemens Celsius W360 system alleviated this problem, after loading the RaggedStone2 card with the appropriate software, a device with the PCI-ID configured in the Core Generator was found by 1spci.

As a next step, the example applications described in the RaggedStone2 documentation and the Xilinx DMA example were tried. Once the card's presence was successfully recognised, the next problem was the absence of sensible data in lspci -vvv. An unassigned pin or a wrong polarity for the reset

signal of the card as well as a possibly broken version of the PCI Express core in ISE version 12.1 were presumably responsible for these problems. After fixing the aforementioned problems and changing the ISE version to 13.1, configuration space data was output in lspci. All further implementation was done based on the ISE 13.1 version of the core and the other tools.

While all my attempts to make the example application from the RaggedStone2 documentation functional have failed, the Xilinx DMA example in [26] worked with a few adaptions. The «xbmd.ko» kernel module contained therein had to be ported to newer kernels and to 32 bit compatibility system calls in 64 bit kernels. With these adaptions the userspace application also included in the Xilinx DMA example code could be successfully used.

Taking the working example application as a basis, several tests in order to verify the function of various parts of the application were done. Another purpose was to familiarise myself with the functioning of the application and PCI Express transactions in general.

To avoid working with the userspace application and kernel module from the Xilinx example application, I first started to implement a bespoke kernel module named «exzess.ko» for the FPGA card. Using that kernel module, writing and reading the device memory of the card as well as allocating DMA memory and having the card write to it was significantly easier. These functions could also be performed by the Xilinx set of application and kernel module, but due to the rather elaborate structure and larger extent of the code, the necessary adaptions would have taken longer.

One specific linux kernel feature, unused by the Xilinx application, simplified matters immensely: device memory can be accessed by files representing the respective device memory areas under the /sys/bus/pci/devices/ hierarchy. Any userspace application with root priviledges can access the files named resource0 through resource5, e.g. using the mmap syscall, thereby mapping the device memory area into the application's address space. Changing the userspace application or just using commonly available tools like dd or hexdump is far easier than frequently having to reload the kernel module.

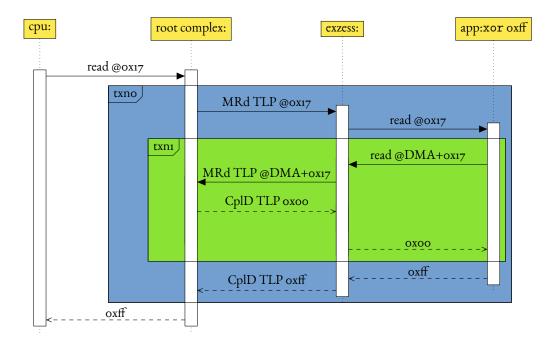

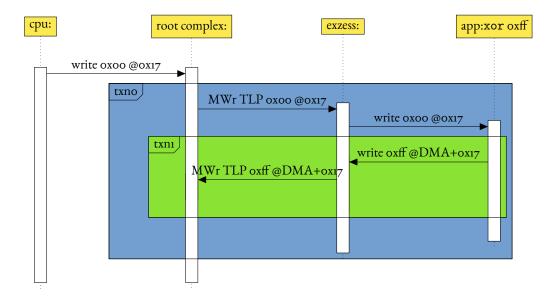

The Xilinx FPGA application was modified in several ways: First to check if reading and writing DMA memory and device memory worked as expected, e.g. by setting or changing memory contents. After initial success with these tests, the implementation of similar nested transactions like the ones shown in figure 4.3 was tried. However, given the structure of the Xilinx example application, this was a much more complicated task. Predominantly because the example application was designed to only support benchmarking DMA accesses. To implement these benchmark accesses, some device memory registers were implemented, holding settings like the DMA base address, the write and read mode and size, the byte pattern to be written or read, the read and write count and a start trigger bit. After the start trigger bit was set, the FPGA started to first write, then read the DMA area in a loop with increasing addresses starting from the base address. After finishing the write-phase, the following read-phase compared the pattern read from memory with the previously written pattern. In the userspace application, the quotient of the bytes written or read and the elapsed time was calculated and shown as the performance value. In this setup, possible reactions to incoming TLPs were limited: Incoming com-

pletions to memory reads were compared against the pattern previously written and then discarded, the data was not intended to be passed on within the FPGA application. The generation of outgoing completions and reactions to writes was limited to the registers in the device memory. Therefore, the creation of outgoing TLPs and the handling of incoming TLPs was, adapted to the requirements, quite simple: The receiving and transmitting parts of the TLP handling were completely independent, except for one «completion needed» bit that reacted to incoming reads to the BAR area by generating a completion. In all other cases, incoming and outgoing TLPs were totally independent of each other, meaning that their handling never necessitated the access to any shared state.

This situation was not easy to change into the required architecture for a more complex and stateful reaction to incoming TLPs like in figure 4.3. To verify that nested transactions were possible, a trivial implementation was successfully done based on the Xilinx code. Yet after this success it had become quite clear than a bespoke implementation of the TLP handling and a generalised application interface would be required.

# 4.4 Bespoke Implementation of TLP Generation and Application Interface

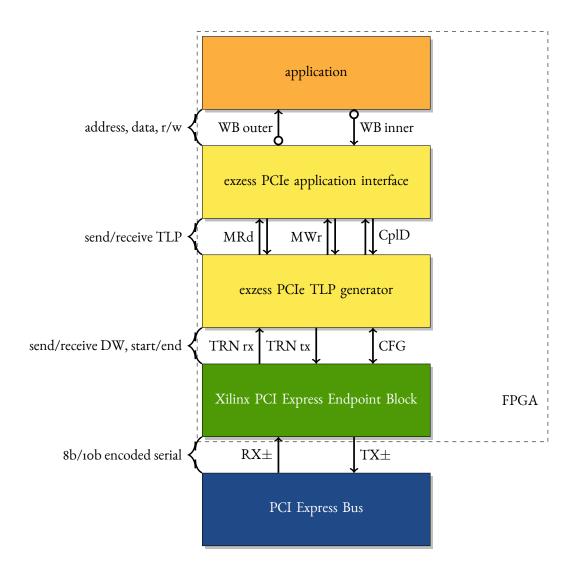

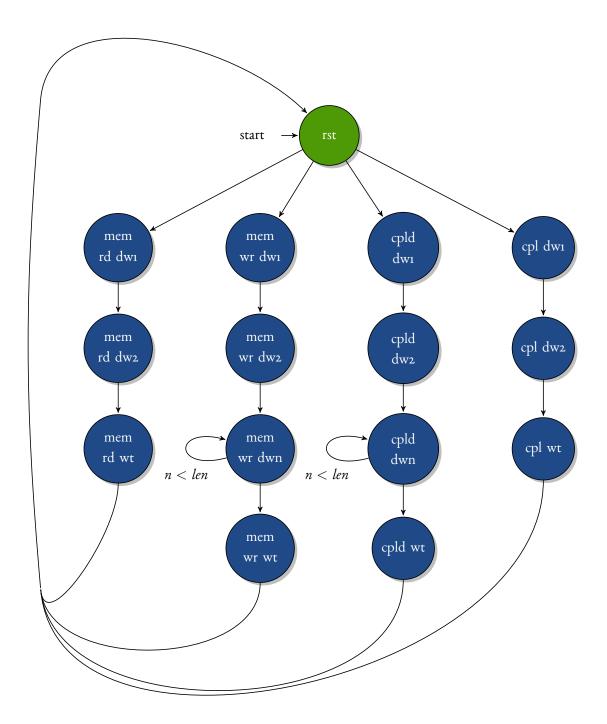

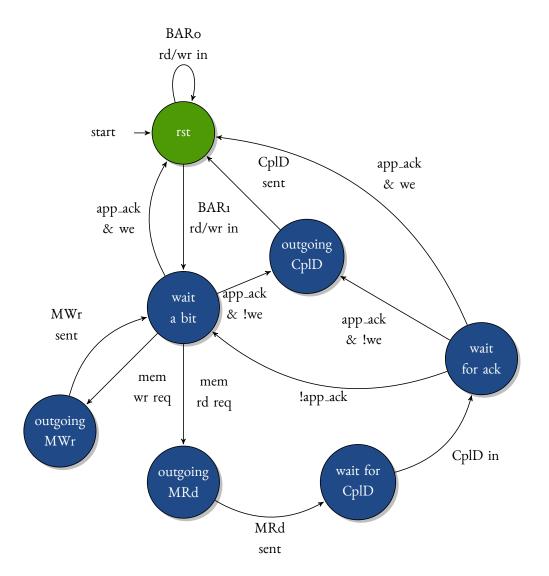

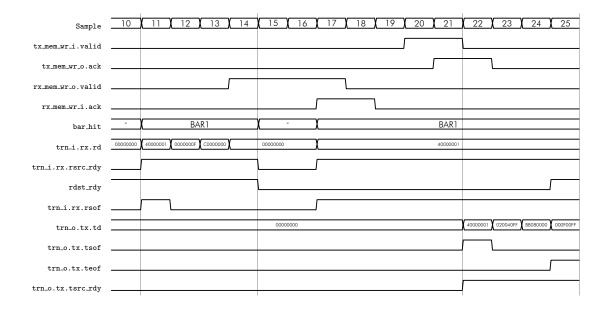

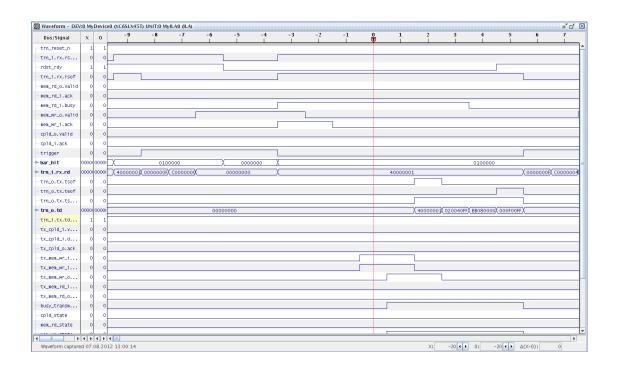

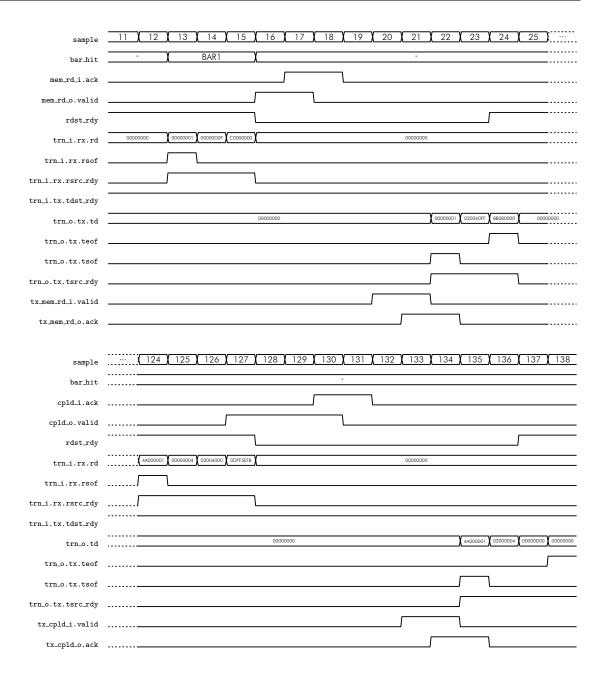

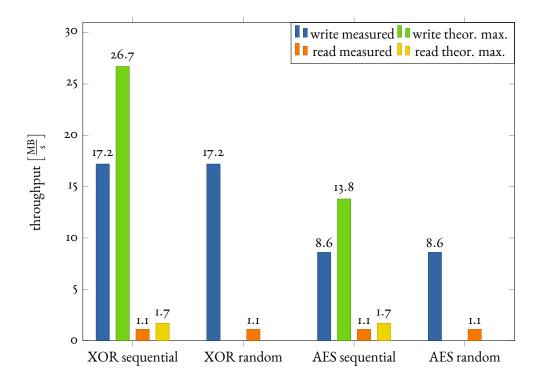

The principal architecture of the new implementation was planned as follows: Starting from the interface the Xilinx PCI Express core provides, modules should be added that provide higher levels of abstraction to the next layer module, until the application module is provided with a simple interface that mainly consists of specifying an address, data and a read or write bit. The module layout that has been chosen for this can be seen in figure 4.2. The following paragraphs will present the function of the modules I have implemented from bottom to top.